MIPI CSI-2 IP

As part of the MIPI (Mobile Industry Processor Interface) standard, MIPI CSI-2 IP supports high-definition image and video streaming, making it an ideal solution for modern cameras, sensors, and imaging systems. With its ability to provide low-power, high-performance connectivity, MIPI CSI-2 IP ensures seamless integration in smartphones, automotive applications, drones, and security systems.

-

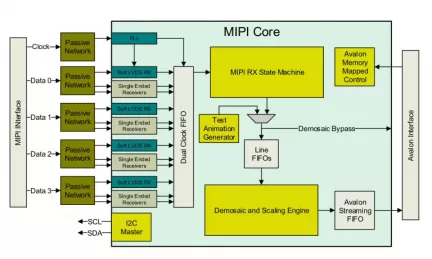

MIPI CSI2 Receiver

- Provides Compatible MIPI D-Phy v1.1 physical layer using FPGA LVDS/LVCMOS IO and passive network

- Supports CSI-2 protocol for unidirectional data transfer

- Compatible with D-PHY Configured for 1 clock and 4 data lanes

- Intended for per-lane clocks rates up to 1 Gbps, depending on device speed grade

-

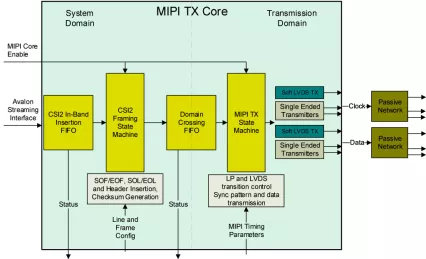

MIPI CSI2 Transceiver

- Provides Compatible MIPI D-Phy v1.1 physical layer using FPGA LVDS/LVCMOS IO and passive network

- Supports CSI-2 protocol for unidirectional data transfer

- Compatible with D-PHY Configured for 1 clock and 1 data lane

- Intended for per-lane clocks rates up to 1 Gbps, depending on device speed grade

-

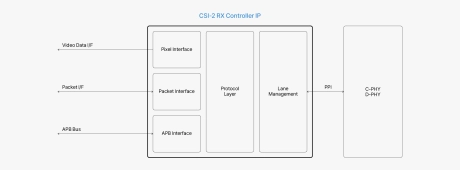

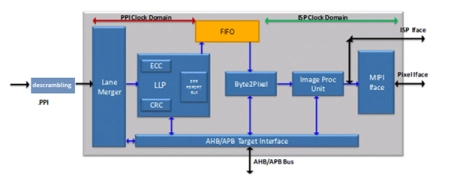

MIPI CSI-2 RX Controller

- Lane merging, virtual channel detection, and programmable data extraction

- Error detection and correction, including packet-level and protocol decoding errors

- Supports all pixel formats defined in the CSI-2 standard

-

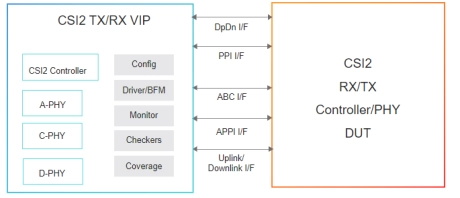

Simulation VIP for MIPI CSI-2

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection at CSI-2, D-PHY, C-PHY and A-PHY levels

- Callbacks access at multiple TX and RX queue points for scoreboarding and data manipulation

-

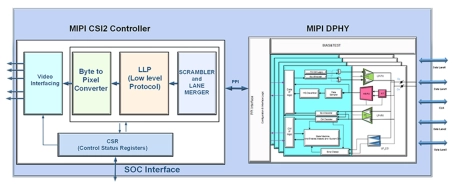

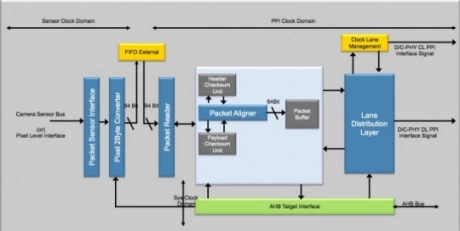

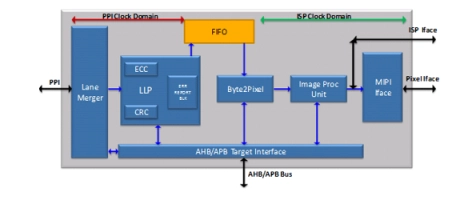

MIPI CSI2 Interface Solution

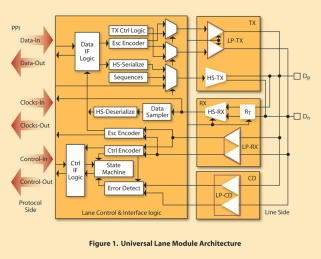

- Brite provides full solution for the MIPI CSI interface, which receives the data from sensors in PHY layer, and then converts the byte data to pixel after lane data mergence.

- Data scramble is an optional feature to decrease the EMI effect.

- A standard PPI interface is implemented for the connection between MIPI PHY and CSI controller. Brite MIPI CSI interface solution supports image applications with varying pixel formats.

-

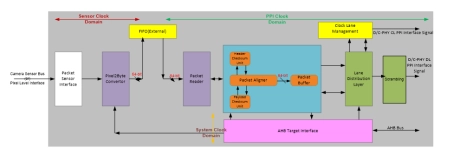

CSI-2 v2.1 Receiver IP

- Fully compliant to MIPI standard

- Small footprint

- Functionality ensured with comprehensive verification

- Product quality proven with silicon

-

CSI-2 v2.1 Transmitter IP

-

Arasan IP Core that functions as a MIPI CSI-2 Transmitter, which typically resides in a mobile platform’s camera module, and communicates over a D-PHY/C-PHY link to a CSI2 Receiver in the applications processor.

-

The Arasan CSI-2 combo IP is MIPI-compliant and provides a standard, scalable, low-power, high-speed interface that supports a wide range of higher image resolutions.

-

-

CSI-2 v1.3 Transmitter IP

- The MIPI compliant IP cores are interface building blocks that simplify interconnect architectures in mobile platforms.

- This leads to smaller footprint, greater interoperability between mobile IP, chips and devices from diverse sources, and lower power and EMI.

-

CSI-2 v1.3 Receiver IP

- The Mobile Connectivity (MIPI) compliant IP cores are interface building blocks that simplify interconnect architectures in mobile platforms.

- This leads to smaller footprint, greater inter-operability between mobile IP, chips and devices from diverse sources and lower power and Electro Magnetic Interface (EMI).

-

MIPI D-PHY IP

- The D-PHY is partitioned into a Digital Module – CIL (Control and Interface Logic) and a Mixed Signal Module. It is provided as a combination of Soft IP views (RTL, and STA Constraints) for Digital Module, and Hard IP views (GDSII/CDL/LEF/LIB) for the Mixed Signal Module.

- This unique offering of Soft and Hard IP permits architectural design flexibility and seamless implementation in customer-specific design flow.