The MIPI CSI-2 Receiver IP Core functions as a MIPI Camera Serial Interface Receiver, between a peripheral device (Camera module) and a host processor (baseband, application engine). The Arasan MIPI CSI-2 Receiver IP provides a standard, scalable, low-power, high-speed interface that supports a wide range of higher image resolutions.

The MIPI CSI-2 Receiver is compliant to MIPI CSI-2 v2.1 specification and supports DPHY v2.1 and the MIPI C-PHY v1.2.

MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

Overview

Key Features

- Use of either D-PHY/C-PHY by user configuration

- Different Configuration allowed for multiple use cases

- 4-Lanes/8-Lanes D-PHY / 3-Lanes C-PHY

- Lane is configurable depending on the bandwidth requirements of the application, up to 8-lanes for DPHY and up to 3-lanes for C-PHY

- High Speed (HS) receiver rates of 182Mbps (80Msps) to 6840Mbps (3Gsps) per lane with C-PHY interface

- High Speed (HS) receiver rates of 80Mbps to 1500Mbps per lane without calibration, 1500Mbps to 2500 Mbps with skew calibration and 2500Mbps to 4500Mbps with equalization in D-PHY interface

- Supports for Ultra Low Power Mode (ULPS)

- Supports for Alternate Low Power State (ALPS) in CPHY mode

- Single (or) Optional Multi-Pixel mode interface to ISP. The multi-pixel mode is used in high bandwidth requirement applications to lower the ISP clock frequency requirement.

- Optional Pixel Level Interface to ISP with HSYNC, VSYNC, DATA and DATA VALID

- Streams the received pixels onto eight data channels (customizable) based on the channel configuration from ISP

- Separate data channel for the short generic packets

- Support for all packet level errors, Protocol Decoding Level errors

- Support for cut-though (or) store and forward mode FIFO. Cut-through mode makes use of shallow Memory for memory critical applications.

- Optional support for Compressed data formats

- Optional support for different error counting

- Pixel formats supported

- RAW data type – RAW6,RAW7,RAW8, RAW10, RAW12, RAW14,RAW16, RAW20

- YUV data type – YUV422-8bit, YUV422-10bit, Legacy YUV420 8-bit,YUV420 10-bit,YUV420 8-bit (Chroma Shifted Pixel Sampling),YUV420 10-bit (Chroma Shifted Pixel Sampling)

- RGB data type – RGB888, RGB666, RGB565, RGB555, RGB444

- All user Defined data types / JPEG

- Generic 8-bit long packet data types

- Host interface for register configuration and monitoring

- Used for programming both CSI-2 and PHY related registers. Reserved address space [0x00 – 0x0F] for the PHY related registers.

- Optional support for the AHB/APB Interface

Benefits

- Fully compliant to MIPI standard

- Small footprint

- Code validated with Spyglass

- Functionality ensured with comprehensive verification

- Product quality proven with silicon

- Premier direct support from Arasan IP core designers

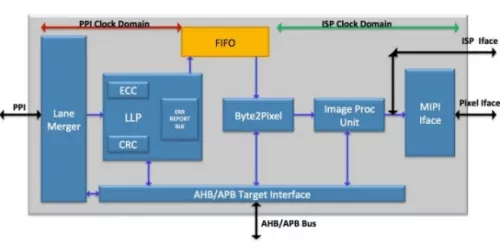

Block Diagram

Deliverables

- Verilog HDL of the IP core

- User guide

- Synthesis scripts

- Lint report

- CDC report

- Verilog test suite

- Gate count estimation available upon request

Technical Specifications

Short description

MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

Vendor

Vendor Name

Maturity

In Production

Availability

Now

Related IPs

- MIPI CSI-2 with C-PHY Verification IP

- MIPI D-PHY v2.1 IP Core

- MIPI CSI-2 Receiver v2.0 Controller IP, Compatible with MIPI C-PHY & D-PHY

- MIPI CSI-2 Receiver v1.1 Controller IP, Compatible with MIPI C-PHY & D-PHY

- MIPI CSI-2 Receiver v1.3 Controller IP, Compatible with MIPI C-PHY & D-PHY

- Simulation VIP for MIPI D-PHY, C-PHY and A-PHY