MIPI C-PHY/D-PHY Combo CSI-2 TX (Transmitter) in TSMC 40ULP

Overview

The MXL-CDPHY-CSI-2-TX-T-40ULP is a high-frequency, low-power, low-cost, source-synchronous, physical layer supporting the MIPI Alliance Specification for D-PHY v2.5 and C-PHY v1.2. The PHY can be configured as a MIPI Master supporting camera interface CSI-2. The PHY supports mobile, IoT, virtual reality, and automotive applications.

Key Features

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v1.2

- Consists of 1 Clock lane and 2 Data lanes in D-PHY mode

- Consists of 2 Data trios in C-PHY mode

- Embedded, high performance, and highly programmable PLL

- Supports both low-power mode and high speed mode with integrated SERDES

- 80 Mbps to 1.5 Gbps data rate per lane in high speed D-PHY mode

- 80 Msps to 1.5 Gsps symbol rate per trio in high speed C-PHY mode

- 10 Mbps data rate in low-power mode

- Low power dissipation

- Testability support

Benefits

- Compatible with both C-PHY v1.2 and D-PHY v2.5 specifications for added flexibility.

- All D-PHY subblocks are reused in C-PHY mode for minimum area overhead.

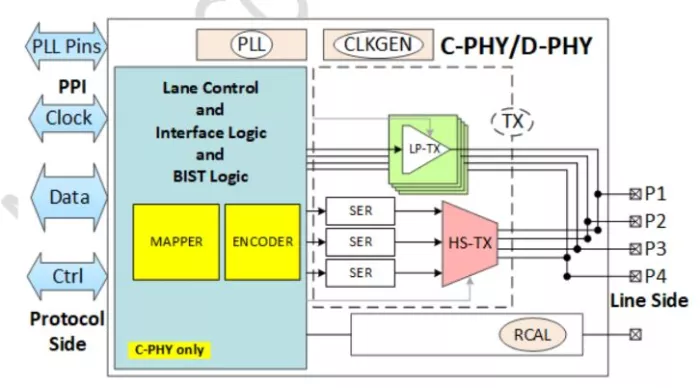

Block Diagram

Applications

- Mobile

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- IBIS Model

- Verilog Model

- Timing Model

- Integration Guidelines

- RTL

- Documentation

- One year support

Technical Specifications

Foundry, Node

TSMC, 40ULP

Maturity

Upon Request

Availability

Upon Request