LZRW3 Data Compression Core

The Lempel-Ziv (LZ) compression methods are among the most popular algorithms for lossless data compression.

Overview

The Lempel-Ziv (LZ) compression methods are among the most popular algorithms for lossless data compression. LZ methods use a table based compression model where table entries are substituted for repeated strings of data.

LZRW3 is a well known LZ-type algorithm developed by Ross Williams in the 1990s which offers a useful combination of high throughput and good compression performance. It also has the advantage of being very efficient to build in hardware, unlike the majority of compression algorithms which tend to favour software implementations.

The Helion LZRW3 core implements the LZRW3 data compression algorithm in Altera FPGA without the need for external memory storage. It is capable of handling data throughputs in excess of 1 Gigabit/sec, and is ideal for use for improving system performance and efficiency in data communications, networking and data storage applications.

Key features

- Implements the LZRW3 lossless data compression algorithm

- Available as Compress only, Expand only, or Compressor/Expander core

- Supports data block sizes from 2K to 32K bytes with data growth protection

- Completely self-contained; does not require off-chip memory

- High performance; capable of data throughputs in excess of 1 Gbps

- Highly optimised for use in Altera Stratix 3 & 4 FPGA technologies

- Ideal for improving system performance in data comms and storage applications

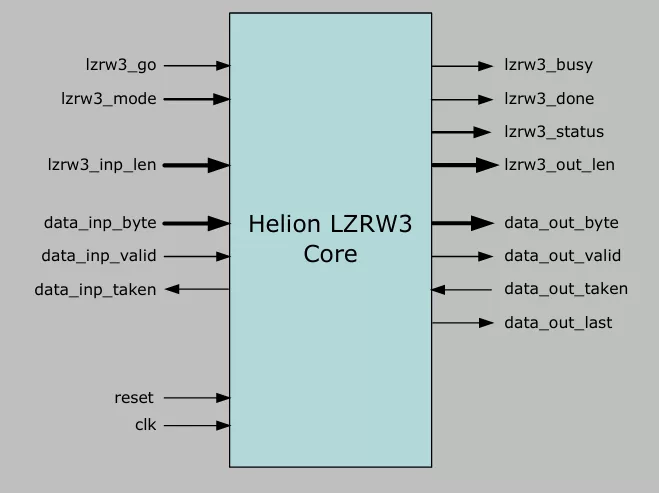

Block Diagram

What’s Included?

- Target specific netlist or fully synthesisable RTL VHDL/Verilog

- VHDL/Verilog simulation model and testbench

- Comprehensive User documentation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Data Compression IP core

Data compression tutorial: Part 3

Firmware Compression for Lower Energy and Faster Boot in IoT Devices

A configurable FPGA-based multi-channel high-definition Video Processing Platform

IP Core for an H.264 Decoder SoC

Digital Associative Memories Based on Hamming Distance and Scalable Multi-Chip Architecture

Frequently asked questions about Data Compression IP

What is LZRW3 Data Compression Core?

LZRW3 Data Compression Core is a Data Compression IP core from Helion Technology Limited listed on Semi IP Hub.

How should engineers evaluate this Data Compression?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Data Compression IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.