LVDS TX+ (Transmitter) in UMC 40LP

Overview

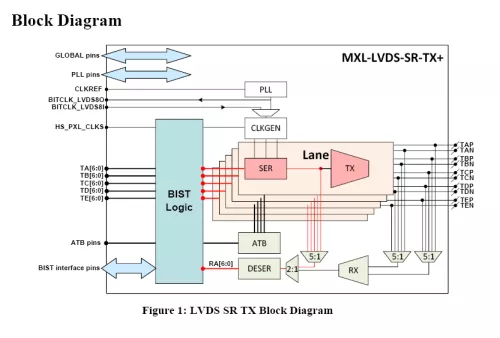

The MXL-LVDS-SR-TX+ is a high performance 4-channel LVDS transmitter implemented using digital CMOS technology. With a maximum transmit clock frequency of 110 MHz, it converts 28 bits of CMOS data into four LVDS data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link. The circuit is designed in a modular fashion and desensitized to process variations resulting in a robust design.

Key Features

- Compatible with TIA/EIA-644 LVDS Standard

- 49 Mbps - 770 Mbps bandwidth/channel

- Up to 3.08 Gbps data throughput

- 7-bit serial data transmitted per pixel clock per channel

- 4 data channels and 1 clock channel

- Configurable extension to 8 data channels to support Dual Pixel mode

- PLL requires no external components

- Analog, Digital DFT and Loopback testability support

Benefits

- Configurable between single-pixel mode with one clock and 4 data lanes or dual-pixel mode with one clock and 8 data lanes, using two LVDS PHY instances. This gives users flexibility to support different types of displays

- Comprehensive embedded DFT features for allowing cost-effective high- volume manufacturing tests

- Supports full-speed loopback testability with minimal area overhead for high-volume manufacturing tests

- One RX are used to test all 4 Transmitters to minimize area overhead

- Two different loopback modes allow isolation of faults and defects

- Analog test bus (ATB) for sensing and forcing internal analog voltages and currents

- Digital test bus for observing PLL clocks and PHY clock outputs

Block Diagram

Applications

- Mobile

- Displays

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- IBIS Model

- Verilog Model

- Timing Model

- Integration Guidelines

- RTL

- Documentation

- One year support

Technical Specifications

Foundry, Node

UMC 40nmLP

Maturity

Silicon Proven

Availability

Now

GLOBALFOUNDRIES

Pre-Silicon:

130nm

SMIC

Pre-Silicon:

130nm

LL

UMC

Pre-Silicon:

40nm

LP