Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks

Overview

Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks

Key Features

- Low noise: high power Supply Rejection Ratio (PSRR): - 65 dB at F < 10 kHz

- Low intrinsic noise: 20 uVRMS at 10 Hz to 20 kHz

- Low Bill-of-Material: optimized in density for the best trade-off for the given output current and input voltage range

- Cost efficient solution compared to external Power Management.

- Compatible with both Tantalum and ceramic capacitors

- Behavioral models: ease integration in SoC and optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation

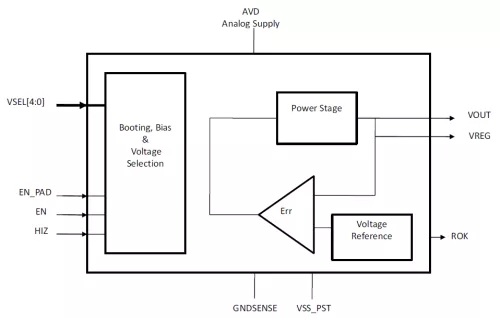

Block Diagram

Technical Specifications

Short description

Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks

Vendor

Vendor Name

Foundry, Node

TSMC 180nm G

Maturity

Pre-silicon

TSMC

Pre-Silicon:

180nm

G

Related IPs

- Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks

- Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks

- Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks

- Linear Regulator, Low-noise optimized for sensitive application such as RF or PLL blocks

- Linear Regulator, Fast load transient respons voltage regulator optimized for sensitive application such as RF blocks

- Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference