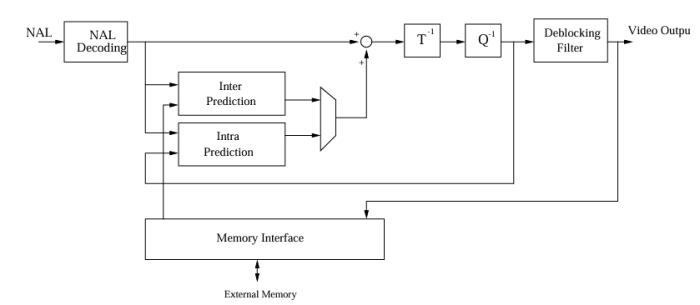

The OL_H264LD core is a hardware implementation of the H.264 baseline video compression algorithm. The core decodes a bitstream produced by the OLH264e encoder and produces a video stream up to the highest HDTV resolution. Simple, fully synchronous design with low gate count.

The OL_H264LD core is a hardware implementation of the H.264 baseline video compression algorithm designed to decode a bitstream created by the OL_H264e core and output progressive video up to HDTV 1920x1080 at 30 fps.

Each block of 16x16 pixels is processed in just 1024 cycles. This means that each pixel is processed in just 4 cycles. Consequently, given an target video stream of resolution X by Y, and frame rate fps, the minimum clock frequency to decode a such bitstream is:

F = 4*X*Y*fps

This allows the core to process the video stream at relatively low clock frequencies. For example, HDTV video of 1920x1080 @ 30 fps requires ~250 MHz, whereas VGA video of 640x480 @ 30 fps requires ~37 MHz.