HDTV H.264/AVC Baseline Video Encoder

The OL_H264e core is a hardware implementation of the H.264 baseline video compression algorithm.

Overview

The OL_H264e core is a hardware implementation of the H.264 baseline video compression algorithm.

The core accepts up to the highest resolution HDTV video stream as input and outputs the encoded bitstream.

Simple, fully synchronous design with low gate count.

The OL_H264e core is a hardware implementation of the H.264 baseline video compression algorithm designed to process HDTV progressive video up to 1920x1080 at 30 fps.

Each block of 16x16 pixels is processed in just 1024 cycles. This means that each pixel is processed in just 4 cycles. Consequently, given an uncompressed video stream of resolution X by Y, and frame rate fps, the minimum clock frequency to process a such video stream is :

F = 4*X*Y*fps

This allows the core to process the video stream at relatively low clock frequencies. For example, HDTV video of 1920x1080 @ 30 fps requires ~250 MHz, whereas VGA video of 640x480 @ 30 fps requires ~37 MHz.

Key features

- Fully compatible with the ITU-T H.264 baseline specification.

- Proven in FPGA : VGA (640x480) at 30 fps in VirtexII-4 demo board.

- Profile level 4.1, can be decoded by Main Profile decoder.

- Supports up to the highest HDTV video resolution (1920x1080 @ 30 fps progressive).

- Very low operational frequency : from ~1.5 MHz for QCIF @ 15 fps to ~250 MHz for 1920x1080 @ 30 fps.

- Single core HDTV support in FPGA : 720p (1280x720) at 30 fps in high end FPGAs (Virtex4) . 4 CIF (704x576) at 30 fps in low end FPGAs (Spartan3-4, slowest speed grade).

- No CPU required for encoding.

- Variable Bit Rate (VBR) and Constant Bit Rate (CBR).

- Very low latency in VBR (~1.1 ms for VGA @ 30 fps).

- Motion vector up to –16.00/+15.75 pixels (search area is 32x32 pixel wide down to quarter pixel).

- Support for most of intra4x4 and all intra16x16 modes.

- Multiple slices support for better error resilience.

- Block skipping logic for lower bitrate.

- Deblocking filter for better quality.

- External memory interface tolerant of high latencies and delays, ideal in a SoC system or in a shared bus with a CPU. The memory interface can be clocked at a different frequency from the ocre for easier integration.

- Supports YUV 4:2:0 video input.

- Min Clock speed = 4 x the raw pixel clock speed.

- Low gate count : from 129K gates + 100 Kbits of RAM for real time VGA encoding to 178 Kgates + 100 Kbits of RAM for real time 1080p encoding.

- Simple, fully synchronous design.

- Available as fully functional and synthesizable VHDL or Verilog soft-core.

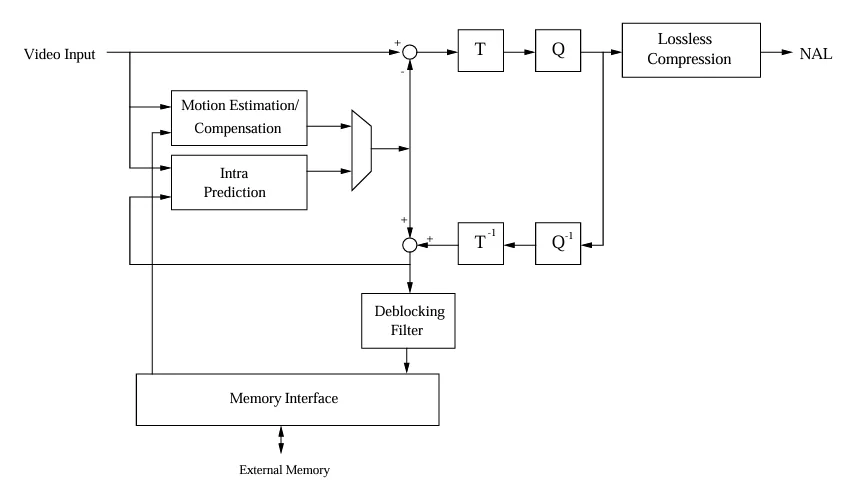

Block Diagram

Applications

- Digital video recorders.

- Video wireless devices.

- Video surveillance systems.

- Hand held HDTV video cameras.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is HDTV H.264/AVC Baseline Video Encoder?

HDTV H.264/AVC Baseline Video Encoder is a Video Processing IP core from Ocean Logic Pty Ltd listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.