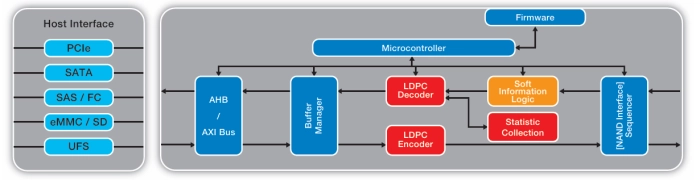

Mobiveil’s LDPC Encoder / Decoder is a flash reliability solution delivering industry leading flash endurance and retention through advanced LDPC error correction at the lowest power and smallest footprint.

LDPC incorporates these advanced technology into a highly scalable flash media-side platform that can be tailored to customers specific application requirements: from smartphones and tablets that require ultra-low power consumption to SSDs for enterprise computing applications that demand the absolute-highest performance.