Dual channel encoder for YUV422 input images, running at full pixel frequency.

This is a raw JPEG encoder engine without header generation, suited for real time and low latency video streaming.

Pixel clocks limits (depending on architecture: 100-150 MHz.

The headers and the packet stream are typically generated by an embedded CPU core and DMA based packet streaming engine, not part of this core.

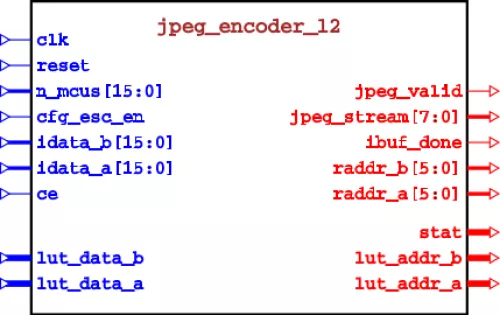

JPEG dual channel encoder

Overview

Key Features

- Baseline JPEG compliant (ITU T.81), Motion JPEG

- Up to 12 bits depth possible (default: 8 bit)

- Super low latency (less than 1/10 of frame duration for rolling shutter cameras)

- Lossy compression by default

- Fully bit and cycle accurate co-simulation model available

- Two-Chip reference design: No RAM, only FPGA and Ethernet Phy required.

- Low power consumption due to clock synchronous, distributed operation

Benefits

- Low power and resource saving solution

- Integrates well into full streaming reference design (IP camera)

- Easy integration as System-on-Chip peripheral with imaging pipeline (Debayer, ...)

- Ready-to-play demo for evaluation on existing reference kits

- Direct integration help based on reference setups

Block Diagram

Applications

- Sub frame latency MJPEG streaming over 100MBit Ethernet to gstreamer or similar video processing pipelines

Deliverables

- Bit file for MJPEG streaming reference design on HDR60 or VIP/EVDK eval kit from Lattice

- Closed netlist for evaluation in own designs (time limit)

- Bit-accurate simulation executables for verification

- VHDL synthesizeable source available under custom source license

Technical Specifications

Maturity

Field proven since 2013

Availability

From 2015

TSMC

Pre-Silicon:

40nm

LP

Related IPs

- JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression

- 8-bit Baseline JPEG Encoder with Optional Video Rate Control

- ADC 12-bit 80Mhz Dual channel - 3.3V

- 8/10/12-bit Extended JPEG Encoder with Optional Video Rate Control

- Dual FPD-link Transmitter, 30/24-bits color, 40-170 Mhz (SVGA/HDTV@120hz) - with 2 independant links capability LVDS SerDes 70:10 channel compression

- Dual FPD-link Transmitter, 30/24-bits color, 40-170 Mhz (SVGA/HDTV@120Hz) - with 2 independant links capability LVDS SerDes 70:10 channel compression