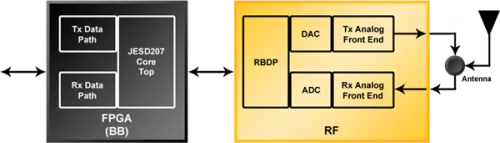

JESD207 is a Radio Front End – Base Band Digital Parallel (RBDP) interface between a Radio Front-end integrated circuit (RFIC) and a Baseband integrated circuit (BBIC). This IP core together with DDR and PLL functionality integrated in the LatticeECP3™ FPGAs implements baseband (BB) side data and control plane paths. It can be used to connect to a radio front-end (RF) transceiver device with integrated analog to digital converter (ADC) and digital to analog converter (DAC).

The Lattice JESD207 IP core is fully compliant to the JESD207 JEDEC specification.

JESD207 IP

Overview

Key Features

- Data path clock and data rate controlled by RFIC (configured by BBIC) up to 90 MHz and 180 MSps

- Data width matched to baseband sample width – 10 or 12 bits

- Raw data path interface transfer bandwidth up to 1.8 or 2.2 Gbps

- Double data rate (DDR) source-synchronous data path transfer timing

- Low latency (single baseband complex sample period) data transfer

- Low implementation complexity

Block Diagram

Technical Specifications

Short description

JESD207 IP

Vendor

Vendor Name