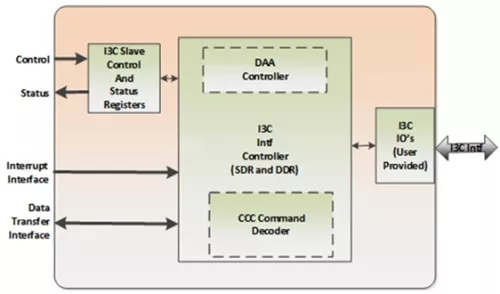

The Arasan I3C Slave Controller IP Core Implements Slave functionality as defined by the MIPI Alliance’s I3C Specification. The I3C bus is used for various sensors in the mobile/automotive system where an I3C Master transfers data and control information between itself and various sensor devices. The I3C Slave Controller IP Core can be easily integrated into the Sensor/Slave devices with minimal gate count.

The I3C Slave controller is highly configurable (synthesis time) to provide an optimal solution based on the Device’s requirements. This include, acting as a legacy I2C device, Support for Dynamic Address Assignment, HDR (any of the three defined HDR Modes) and a configurable FIFO for data transfers. In addition, optional I3C slave functions like Interrupt generation, Hot-Join request generation and advanced slave with secondary master capabilities can be configured for more complex slaves. Also, the I3C Slave Controller IP provides direct signalling to connect to the IO Buffers (SCL and SDA). Please note that the User need to provide appropriate IO buffers to meet the I3C specification.

The I3C Slave controller implements support for legacy I2C Slave functionality, Open-drain and Push-pull operation of I3C Interface, and Dynamic Addressing support. The I3C Slave Controller supports the required SDR mode with Clock frequency of up to 12.5 MHz and optionally the any or all of the three HDR modes as defined by the I3C Specification. The included 16 byte FIFO (Configurable) is used to handle data transfers between IP and the Application.

I3C Slave Controller

Overview

Key Features

- Compliant with MIPI I3C Specification Rev 1.0

- Supports up to 12.5 MHz operation using Push-Pull

- Open-Drain and Push-pull type transactions (as required)

- Acts as a legacy I2C Slave while supporting Legacy I2C Messaging and protocol

- Participates in Dynamic Addressing while supporting Static Addressing for Legacy I2C mode

- I2C-like Single Data Rate Messaging (SDR)

- Optional High Data Rate Messaging Modes (HDR) (Synthesis time configuration)

- Optional support

- Secondary Master function

- Transmission of In-band Interrupt

- Hot-Join Request Generation

- Synchronous Timing Support and Asynchronous Time Stamping

- APB Target Interface for Configuring/Controlling the IP with Interrupt output

- Small 16-byte (Configurable) FIFO for transferring data Slave Controller and the Application

Block Diagram

Deliverables

- RMM compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

- Validated with 3rd Party UVM-based Slave VIP and available as an additional option

Technical Specifications

Maturity

Silicon proven

Availability

NOW