SDIO/SD Memory/MMC Slave Controller

The SD Slave Controller is designed to reside within an SD memory, SDIO, or SD Combo Card.

Overview

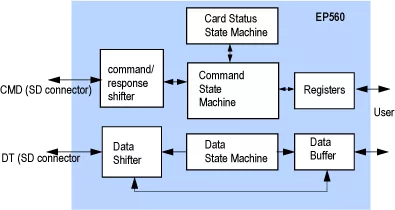

The SD Slave Controller is designed to reside within an SD memory, SDIO, or SD Combo Card. It serves as an interface between the SD bus and user logic that provides the actual function of the card. It is designed to integrate with user logic to make various devices using the SD bus protocol, such as storage or wireless network card.

The SD slave controller supports both 1 and 4 bit SD interface (up to 8 bits in optional MMC support) and SPI mode. Data rate of up to 25Mbyte/sec (200Mbs) can be realized with SD interface. Features such as plug and play, auto-detection, error correction, write protection are standard with SD card interface and are supported.

As a slave device, the SD slave controller receives commands from the host through the SD interface. Most of the commands are processed locally by the controller without any help from the user logic. The majority of the standard SD register set is also implemented within the slave controller and process by the core without help from the user logic.

In case of memory or IO access that needs to be forwarded to the user logic, the slave controller handles all the SD bus protocol and presents the request to the user logic as simple read and write request through parallel address and data buses. Burst transfer of up to 2048 bytes per transfer and user defined wait states are supported on the user interface to maximize data bandwidth. The slave controller also contains data buffer to match the speed differences between the user interface and the SD interface. It allows a much more efficient use of the user interface.

SD Combo card and multi-function cards are supports by the EP560. With Combo card and multi-function, one user interface is dedicated for each function so all functions can operate in parallel.

With the EP560, SD card design can be realized with very little development cost. The designer can add SD memory and SDIO interface capability to the design by simply adding the EP560 module without changing the rest of the system architecture.

Key features

- Compatible with SD/SDIO specification 2.0 with 1 and 4 bit data transfer.

- Option to support MMC 8-bit data width.

- Support SD, SPI and optional MMC bus protocol.

- Support for both standard capacity and high capacity (SDHC) memory cards.

- Supports high speed mode up to maximum transfer rate of 25Mbyte/sec for SD and 50Mbyte/sec for MMC.

- Simple 32-bit bus master interface to DMA data into user memory space.

- Selectable maximum block size from 512 to 16Kbytes.

- Each IO function includes up to 4096 bytes of data buffer.

- Process most commands automatically without user interference.

- Contains SD memory/SDIO standard slave register set.

- Hardware CRC generation and detection.

- Supports multi-function SD cards, suspend and resume, read wait, block transfers, and SDIO interrupts.

- Password Protection for SD cards.

- Options for AHB, APB, PLB, Wishbone, SH4, Avalon and Generic user interface.

- Options for interrupt-based user interface.

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

- Shorten Time-to-market

- Eliminate Design Risks

- Reduce Development Costs

Learn more about SD / eMMC Controller IP core

Virtual Prototyping Platform with Flash Memory

Allowing server-class storage in embedded applications

UFS Goes Mainstream

Universal Flash Storage: Mobilize Your Data

Frequently asked questions about SD / eMMC Controller IP cores

What is SDIO/SD Memory/MMC Slave Controller?

SDIO/SD Memory/MMC Slave Controller is a SD / eMMC Controller IP core from Eureka Technology, Inc. listed on Semi IP Hub.

How should engineers evaluate this SD / eMMC Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SD / eMMC Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.