H8/300 CPU IP ( 8-bit CPU IP )

H8/300 is a high speed 8-bit CPU with an internal 16-bit architecture.

Overview

H8/300 is a high speed 8-bit CPU with an internal 16-bit architecture.

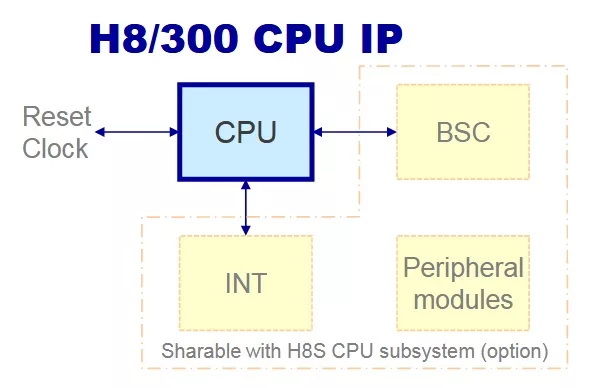

H8/300 CPU IP is compatible with H8S CPU subsystem IP (H8S C200) on system, bus and interrupt interface. So, it can be used in place of H8S CPU with other peripheral modules of optional information packages. It can optimize CPU subsystem gate size for small systems.

Its instruction set is compatible H8/300 and H8/300L series microcontroller products.

Key features

- Small gate size

- Common interface with H8S CPU subsystem IP

- system (reset and clock) interface

- bus interface

- interrupt interface

- Sharable peripheral modules (option) with H8S CPU subsystem

- Applicable to various processes and FPGAs

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is H8/300 CPU IP ( 8-bit CPU IP )?

H8/300 CPU IP ( 8-bit CPU IP ) is a CPU IP core from Renesas listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.