General Purpose I/O controller, fully configurable.

Overview

Beyond GPIO IP core is user-programmable general-purpose I/O controller. Its use is to implement functions that are not implemented with the dedicated controllers in a system and require simple input and/or output software controlled signals.

Key Features

- Number of general-purpose I/O signals is user selectable and can be in range from 1 to 32. For more I/Os several GPIO cores can be used in parallel

- All general-purpose I/O signals can be bi-directional (external bi-directional I/O cells are required in this case)

- All general-purpose I/O signals can be three-stated or open-drain enabled (external three-state or open-drain I/O cells are required in this case)

- General-Purpose I/O signals programmed as inputs can cause an interrupt request to the CPU

- General-purpose I/O signals programmed as inputs can be registered at raising edge of system clock or at user programmed edge of external clock

- All general-purpose I/O signals are programmed as inputs at hardware reset

- Auxiliary inputs to GPIO core to bypass outputs from RGPIO_OUT register

- Alternative input reference clock signal from external interface

- Extremely configurable (implementation of registers, external clock inverted versus negedge flip-flops etc.)

Benefits

- Safe: production silicon proven

- Small: compact, versatile RTL

- Easy: fully documented, with operational examples

- Versatile: fully RTL configurable, software programmable

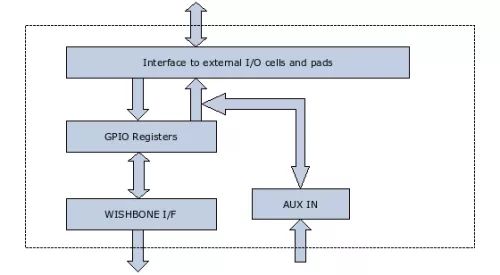

Block Diagram

Applications

- Embedded

- Portable and wireless

- Home entertainment consumer electronics

Deliverables

- Full Verilog RTL source

- Extensive Test Bench

- Documentation

- Linux Driver

- Free Engineering support

Technical Specifications

Short description

General Purpose I/O controller, fully configurable.

Vendor

Vendor Name

Foundry, Node

Process independent

Maturity

In volume production silicon

Availability

Now