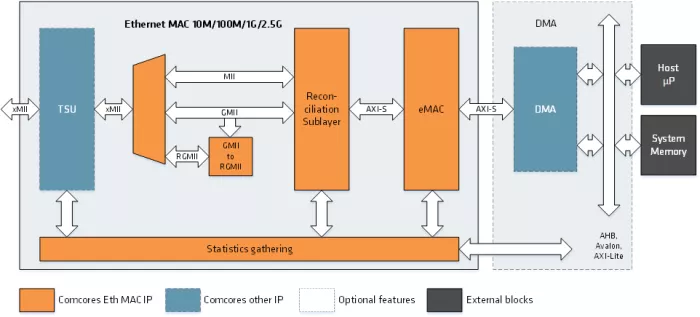

Ethernet MAC 10M/100M/1G/2.5G IP is a solution that enables the host to communicate data using the IEEE 802.3 standard for 10M, 100M, 1G, 2.5G speeds and is suited for use in networking equipment such as switches and routers. The Client-side interface for the IP is AXI-S and the Ethernet MAC IP comes with GMII, RGMII or MII interfaces on the PHY side.

The Ethernet MAC 10M/100M/1G/2.5G IP features a compact and low latency solution, it is highly configurable and can optionally include IEEE 1588 Timestamping Unit (TSU). The Silicon agnostic Ethernet MAC IP, suitable for ASICs and FPGAs, is prepared for easy integration with Ethernet PCS 10M/ 100M/1G/2.5G IP from Comcores.