The new Andes Technology E8 CPU processor core targets Internet of Things (IoT) applications with the unique Andes Custom Extension™ (ACE) on a power-efficient compact embedded controller. SoC designs for IoT devices demand low power consumption in combination with high performance to handle compute intensive functions such as processing sensor data and wireless protocol stacks. The E8's unique ACE environment enables designers to specify the architectural element that makes the core ideal for IoT applications. With Andes' Custom-OPtimized Instruction deveLOpment Tools (COPILOT), designers can create custom instructions that differentiate their design from competitive offerings, which are based on standard instruction set processors. By adding special instructions, not easily discoverable by hackers, ACE also provides stronger security to a design.

Another E8 feature, FlashFetch, boosts performance while saving power. FlashFetch consists of a small amount of buffer near the processor core that enables repetitive functions to be executed efficiently thus eliminating power consuming flash memory accesses. With a three-stage pipeline, the E8 can achieve 1.82 DMIPS per MHz, which is far higher performance than other 32-bit alternatives while the power consumption and gate-count are as low as 8-bit controllers.

Efficient 32-bit Processor with Custom Instructions

Overview

Key Features

- Best in its class per-MHz performance

- Andes Custom Extension™ (ACE) for significant performance efficiency boost

- Small footprint with low gate count and high code density

- Speed-up and power reduction for Flash accesses by FlashFetch technology

Benefits

- Performance

- 16/32-bit mixable instruction format for compacting code density

- Branch predication to speed up loop control

- Return address stack to speed up procedure returns

- Low-latency vectored interrupt for real-time performance

- Completion of most 32-bit operations in one cycle

- Single-cycle capable for most Local Memory and AHB bus accesses

- FlashFetch technology to accelerate internal parallel and/or external SPI flash memory

- Advanced CoDense™ technology to reduce program code size

- Support for Andes Custom Extension™ (ACE).

- Flexibility

- Easy arrangement of preemptive interrupts

- Memory-mapped I/O space

- All-C Embedded Programming

- Stack protection HW to help determining stack size, and detecting runtime overflow error

- Optional boot-up from instruction Local Memory

- Processor state bus to simplify SoC design and debugging

- Configurable big or little endian support

- Several configurations to trade off between core size and performance requirements

- Power Management

- Extensively clock-gated pipeline

- Low power modes initiated by SW or SoC

- N:1 core/bus clock ratios

- PowerBrake technology to reduce peak power consumption

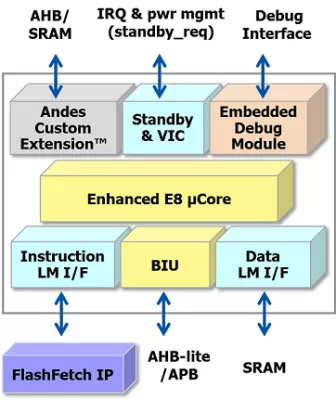

Block Diagram

Applications

- Connectivity device

- Sensor hub

- Wearable device

- Smart meter

- Storage device

- Touch screen controller

- Battery management

- Sensor-less motor driver

Technical Specifications

Short description

Efficient 32-bit Processor with Custom Instructions

Vendor

Vendor Name

Related IPs

- ARC HS45D 32-bit, dual-issue processor core, ARCv2DSP ISA, with 100+ DSP instructions for embedded applications

- ARC HS47D 32-bit, dual-issue processor core, ARCv2DSP ISA, with 100+ DSP instructions and I&D cache

- 32-bit SPARC V8 processor

- 32-Bit SPARC V8 Processor

- 32-bit Deeply Embedded Processor

- 32-bit Basic Application Processor