Deep capture / high visibility Debug IP for Xilinx FPGA

Overview

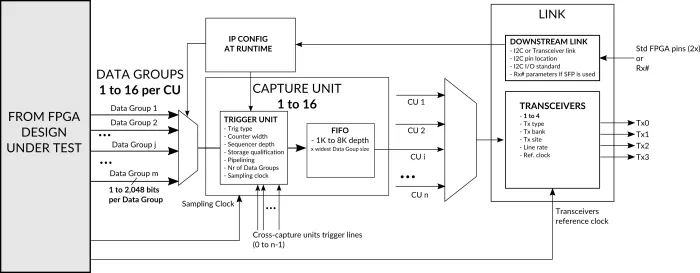

The customizable EXOSTIV IP core is a logic analyzer core that can be used to monitor the internal signals of an FPGA design without having to store the full trace data in the FPGA. The EXOSTIV IP core uses the FPGA transeivers as a high bandwidth channel to an external memory (in EXOSTIV Probe). The IP includes many advanced features for extending visibility on FPGA running at speed of operation- including data group definition and multiplexing, boolean trigger equations, data qualification (data filtering) and edge transition triggers. Because EXOSTIV IP core is synchronous to the design being monitored, all design clock constraints that are applied to your design are also applied to the components inside IP Core. EXOSTIV IP can be inserted at RTL level or automatically in the design netlist, thanks to the accompanying EXOSTIV Dashboard software integration with the FPGA vendor tool.

Key Features

- Configurable upstream link, up to 4 transceivers at 12.5 Gbps each.

- Downstream link to configure IP triggers and data group selection without the need to re-implement the instrumented design.

- Up to 16 configurable 'Capture Units'

- Up to 16 multiplexed Data Groups per Capture Unit

- Up to 2,048 nodes per Data Group

- Up to 32k simultaneously observable nodes

- Multi-clock domain support

- Cross-capture unit trigger lines

Benefits

- Extreme visbility on FPGA running at speed of operation

- Flexible IP insertion options: in RTL or automatically in target design netlist (after synthesis)

- Efficient use of FPGA resources: the impact on the FPGA memory does not grow with the size of the capture.

- Extended visibility over time - with the proper settings, the capture can span to hours of real FPGA operating times, from start to end (interrupted capture mode)

- Real-world visibility level with a total of 8 GB of trace for a single capture.

Block Diagram

Applications

- FPGA debug and verification

Deliverables

- Complete FPGA debugging solution, including EXOSTIV Dashboard software (Linux, Windows, Mac) for EXOSTIV IP setup and insertion - and for EXOSTIV IP control for trace data extraction at run-time.

- Includes EXOSTIV Probe for data extraction from target FPGA at run-time.

- Includes terabyte-capable Myriad waveform viewer.

Technical Specifications

Short description

Deep capture / high visibility Debug IP for Xilinx FPGA

Vendor

Vendor Name

Availability

Now

Related IPs

- Deep capture / high visibility Debug IP for Intel FPGA

- Multi-constellation and Multi-frequency Correlators Soft GNSS IP for high sensitivity and high accuracy GNSS receivers

- High Channel Count DMA IP Core for PCI-Express

- High performance-efficient deep learning accelerator for edge and end-point inference

- MSP7-32 MACsec IP core for FPGA or ASIC

- OpenGL ES 2.0 3D graphics IP core for FPGAs and ASICs