Multi-constellation and Multi-frequency Correlators Soft GNSS IP for high sensitivity and high accuracy GNSS receivers

The MGNSS IP (GNSS IP) is a silicon proven, AHB compliant, all-in view, Multi-constellation and Multi-frequency GNSS baseband IP …

Overview

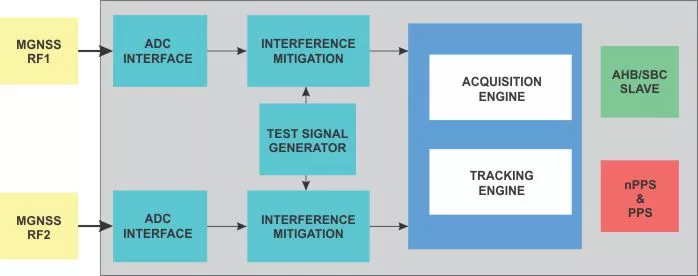

The MGNSS IP (GNSS IP) is a silicon proven, AHB compliant, all-in view, Multi-constellation and Multi-frequency GNSS baseband IP core for integration in GNSS and Application SoCs for Automotive, Smartphones, Precision and IoT applications.

The IP core is highly configurable to support any of the legacy, modernized, and potential future GNSS signals of all available constellations, concurrently or sequentially based on the need of the application. A reduced version of the IP, MGNSS – B1 GNSS IP is available for IoT applications.

It also supports processing of two RF channels offering dual frequency GNSS capability, along with superior immunity features against pulsed and multi-tone interference.

The feature rich, energy efficient baseband provides ultra-fast acquisition and precision tracking performance. The unique baseband architecture provides configurability for very low power applications with reduced sampling rates, select signals, and power-down modes.

Key features

- 64 parallel GNSS signal tracking channels with accurate and precise measurements

- Massive and wide bandwidth correlators enable fast acquisition and high precision

- Supports all signals in L1, L2, L5 and S band frequencies from GPS, GALILEO, GLONASS, BeiDou, QZSS, IRNSS, and SBAS constellations

- Efficient and generic PRN code handling architecture to support future signal structures

- Multi-tone continuous wave interference mitigation and pulsed interference mitigation to enable receiver to operate in intentional or unintentional interference environment

- Processes ADC output from one or two RF front-ends

- Enables PPP and RTK positioning

- Up to 1KHz measurement rate

- Measurement generation on external event or internal 1PPS event

- Battery Backed Counter to maintain GNSS time

- AMBA compliant AHB or Synchronous Parallel Bus interface to CPU

- Optional internal signal generator for faster verification and validation

- Configurable ADC interface – SDR (sampled data on rising edge), DDR (sampled data on rising and falling), various sampling frequencies, real or complex samples, 1-bit to 5-bit ADC data processing

- Patented architecture for lower power and lower logic area

- Comprehensive power-down modes to reduce power consumption depending on the application

- Completely synchronous design with RMM guidelines

Block Diagram

Benefits

- Direct support from Accord for IP integration

- Optional customization Services for AGPS, DR, INS integration as well as for ASIC conversion

- FPGA/ASIC platform for IP evaluation

What’s Included?

- Fully synthesizable and technology independent RTL in VHDL

- Compatible executable binary file for highly configurable GNSS receiver software

- Synthesis scripts along with timing constraints

- Verification environment including the test benches, input and expected output files, execution and analysis scripts

- RTL IP integration manual

- FPGA/ASIC evaluation platform for testing the performance of the IP

- API manual for GNSS library

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about GNSS IP core

Delivering timing accuracy in 5G networks

Where Innovation Is Happening in Geolocation. Part 1: Signal Processing

Decisions, decisions: Hardware accelerator or DSP?

Precisely positioned for autonomous success: Arm and Swift Navigation

New Protocol (NB- IoT) Requires New DSP IP and New Business Model

Frequently asked questions about GNSS IP cores

What is Multi-constellation and Multi-frequency Correlators Soft GNSS IP for high sensitivity and high accuracy GNSS receivers?

Multi-constellation and Multi-frequency Correlators Soft GNSS IP for high sensitivity and high accuracy GNSS receivers is a GNSS IP core from Accord Software and Systems Pvt Ltd listed on Semi IP Hub.

How should engineers evaluate this GNSS?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GNSS IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.