Cortus have applied their many years of processor design expertise to the RISC-V ISA. Concentrating on the needs of the embedded designer and leveraging the success of their APS family of processors.

The APS3V processor offers the RISC-V ISA RV32IMC features, with the full integer instruction set, compressed instructions and multiply and divide. In addition it implements the privilege features with Machine and User modes.

The Cortus APS3V processor is designed to be both power and silicon efficient. The standard implementation requires 17 000 gates.

The four stage pipeline offers a good compromise between throughput and maximum operating frequency, for example in 40 nm an Fmax of at least 1 GHz max can be achieved.

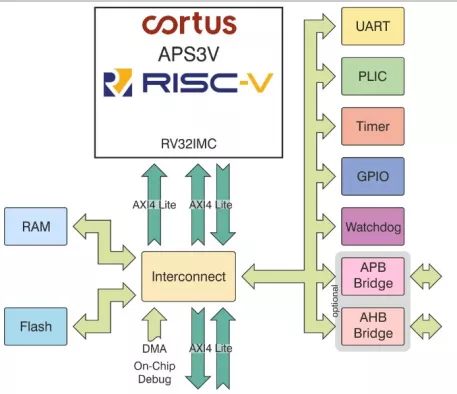

The Cortus APS3V processor features a Harvard architecture with AXI4 Lite bus interfaces. This ensures wide compatibility with other peripheral IP, allowing the standard peripherals from Cortus to be complemented by other IP.

Full debug support is implemented through Cortus’ standard debug interface and tools (GDB and OpenOCD).

Compact Implementation of the RISC-V RV32IMC ISA

Overview

Key Features

- RISC-V 32 bit ISA (RV32)

- Integer Instruction Set (I)

- Compressed Instruction Set (C)

- Integer Multiply & Divide (M)

- Machine and User Modes

- 4 Stage Pipeline

- AXI4 Lite Bus (Instruction and Data)

- Small Silicon Footprint

- Full Peripheral Set

- Hardware Breakpoints

- Full Toolchain and IDE

Benefits

- The Cortus APS3V processor is designed to be both power and silicon efficient. The standard implementation requires 17 000 gates.

- The four stage pipeline offers a good compromise between throughput and maximum operating frequency, for example in 40 nm an Fmax of at least 1 GHz max can be achieved.

Block Diagram

Applications

- Embedded Control

- Encryption and Decryption

- Wireless and Wireline Communication

- Sensor Fusion

- Machine Vision

- Dual and Multi-core Systems

Deliverables

- Full Verilog Source Code

- Full Toolchain

- Graphical Development Environment

- Debugger

- Standard Peripherals

- Full Documentation

- Complete Integration Guide

- Supplied as Part of a Design Services Contract

Technical Specifications

Short description

Compact Implementation of the RISC-V RV32IMC ISA

Vendor

Vendor Name

Foundry, Node

All

Related IPs

- Compact Implementation of the RISC-V RV32IMAC ISA

- Implementation of the RISC-V RV64GC ISA

- Compact Implementation of the RISC-V RV32EMC ISA

- 64-bit embedded processor, fully compliant with the RISC-V ISA

- 8-stage, dual-issue, highly efficient in-order pipeline compatible with the RISC-V RV64GCV ISA

- High-performance implementation of Z80/Z180 instruction set