Vendor:

Microtronix Datacom Ltd.

Category:

Video Transport

Camera Link Aligner

The Microtronix Camera Link Aligner IP Core is designed for building Frame Grabber (Receiver) Medium & Full Channel Link™ interfa…

Overview

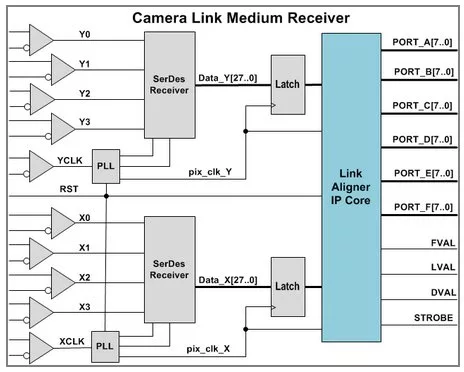

The Microtronix Camera Link Aligner IP Core is designed for building Frame Grabber (Receiver) Medium & Full Channel Link™ interfaces in conjunction with the SerDes blocks of Altera FPGA devices. The core includes supports for the adjunct Camera Link serial control and data communication signals.

The Link Aligner synchronizes the data between Channel Links in Medium and Full Camera Link Frame Grabber configurations. The using FIFO's the ALigner synchronizes the data across Links by removing delays caused by phase differences of the clock sources between Channel Links or cable length mismatches. The Link Aligner block compares the LVAL signal from each Channel Link and using FIFO's auto adjusts the our delays to bring the links into phase alignment. It also synchronizes data at the output Ports to the STROBE/XCLK clock.

The IP also includes a Power Over Camera Link (PoCL) SafePower logic block, which when implemented with supporting hardware, allows a Frame Grabber to provide DC power to PoCL cameras and while still remaining compatible with non-PoCL cameras. The SafePower IP block works with the PoCL circuitry on the Microtronix Camera Link Receiver HSMC Daughter Card.

The Link Aligner synchronizes the data between Channel Links in Medium and Full Camera Link Frame Grabber configurations. The using FIFO's the ALigner synchronizes the data across Links by removing delays caused by phase differences of the clock sources between Channel Links or cable length mismatches. The Link Aligner block compares the LVAL signal from each Channel Link and using FIFO's auto adjusts the our delays to bring the links into phase alignment. It also synchronizes data at the output Ports to the STROBE/XCLK clock.

The IP also includes a Power Over Camera Link (PoCL) SafePower logic block, which when implemented with supporting hardware, allows a Frame Grabber to provide DC power to PoCL cameras and while still remaining compatible with non-PoCL cameras. The SafePower IP block works with the PoCL circuitry on the Microtronix Camera Link Receiver HSMC Daughter Card.

Key features

- Auto Link Aligner for 8-bit, 10-tap Base, Medium & Full Frame Grabber configurations

- Supports 64-bit and 80-bit extended Full configurations

- Pixel clock rates to 85 MHz.

- Power Over Camera Link (PoCL) SafePower

- Bi-directional serial Camera Link communication

- Java configuration GUI streamlines Quartus design process

- Leverages the SerDes blocks of Cyclone V, Arria V and Stratix IV/V devices for building Frame Grabber systems

Block Diagram

1605609 block diagram

Applications

- The Camera Link Aligner IP Core is targeted at Frame Grabber applications including; industrial vision systems, high-speed video interconnects, video capture devices, interface conversion, and video processing equipment.

What’s Included?

- The IP is supplied as an FTP download.

- It includes:

- Java Configuration GUI

- TimeQuest timing analyzer Synopsis Design Constraint (SDC) file

- VHDL ModelSim library

- User documentation

- Quartus Reference Design supporting a Camera Link Medium & Full receiver configurations

- Includes perpetual IP core license with 1 year of updates

- The IP Core license is perpetual and does not expire. It is available either as a Node Locked or Floating Server.

- Node Locked: Supports a single user. It is tied to the NIC ID of a PC.

- Floating Server: Supports multiple users (typically 2 or 5 seats)

Specifications

Identity

Part Number

1605609

Vendor

Microtronix Datacom Ltd.

Type

Silicon IP

Files

Note: some files may require an NDA depending on provider policy.

Provider

Microtronix Datacom Ltd.

HQ:

Canada

Microtronix began as a design and embedded engineering firm for custom networking equipment for the Telco marketplace, pioneering the X25 protocol. Today, Microtronix uses these same engineering skills to develop and support their own line of embedded products, specializing in the rapid development of FPGA based hardware, IP cores, printed circuit board, and software solutions for embedded products. Microtronix provides a turnkey design-development service, with proven expertise in taking products from initial concept through to production.

Microtronix also provides embedded engineering design services for these technologies either on an hourly basis or through a fixed price quotation.

By design, all Microtronix solutions are engineered to be cost effective and exceed their requirements for service, quality, and function.

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Tfox

Enabling High Performance SoCs Through Multi-Die Re-use

This paper gives a high-level overview of a technique for rapid design of new IC designs using multiple dice packaged in a variety of aggregations allowing for differnent performance levels and price points to be achieved. The technique relies on a new high-bandwidth low pin-count communication channel between two or more dice.

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

This paper presents the interconnect solution adopted for an HDTV SoC developed in HVD division of STM. The SoC is a one-chip satellite HDTV set-top box IC developed in 65nm technology. The interconnect of this HDTV SoC is the first in STM implementing a mixed architecture based on the circuit-switched interconnect named STBus and the new NoC interconnect named VSTNoC.

Steps for Delivering Multimedia Over 5 GHz WLANs

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

The H.264 Scalable Video Codec (SVC) reduces network bandwidth, eliminates transcoding, and simplifies storage management. Here's how it works.

Frequently asked questions about Video Transport IP cores

What is Camera Link Aligner?

Camera Link Aligner is a Video Transport IP core from Microtronix Datacom Ltd. listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.