APB I2C master and slave

Overview

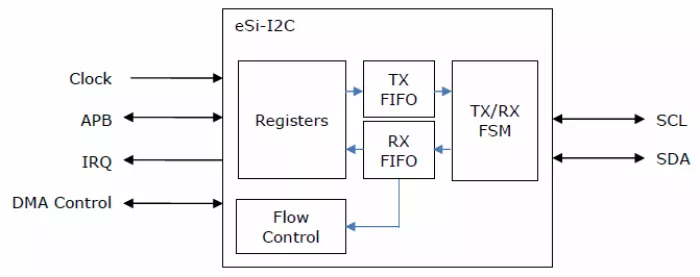

The eSi-I2C core implements the I2C two-wire protocol. It supports operation as both an I2C master and slave. The I2C is supplied with an AMBA APB slave interface and so can be driven by software or via DMA.

Key Features

- Multi-master / slave operation.

- Clock stretching.

- 7 and 10-bit addresses.

- Programmable bit rate.

- Programmable digital filtering for SDA and SDL inputs.

- Configurable TX and RX FIFOs.

- AMBA 3 APB slave interface.

- DMA flow-control interface.

Block Diagram

Deliverables

- Verilog RTL

- Testbench

- Simulation and synthesis scripts

- Documentation

- C API

Technical Specifications

Maturity

Silicon proven in multiple products

Availability

Immediate

Related IPs

- I2C Controller IP- Master / Slave, Parameterized FIFO, APB Bus

- I2C Controller IP – Slave, Parameterized FIFO, APB Master Interface (I2C2APB)

- I2C Master and Slave

- Master and Slave SPI Bus Controller

- I2C Controller IP – Master, Parameterized FIFO, APB Bus

- I2C Controller IP- Master / Slave, Parameterized FIFO, AXI Bus