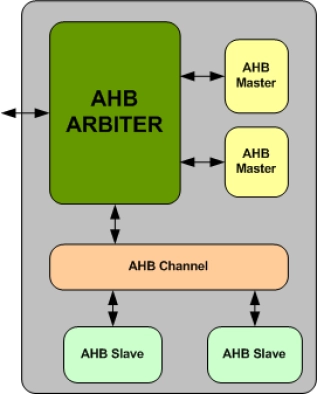

AHB Arbiter IP core is compliant with AMBA AHB Specification. Through its compatibility, it provides a simple interface to a wide range of low-cost devices.AHB Arbiter IIP is proven in FPGA environment.

AHB Arbiter IIP is supported natively in Verilog and VHDL