AHB Single Channel DMA Controller

The AHB Single Channel DMA Controller core is a configurable single channel direct memory access controller.

Overview

The AHB Single Channel DMA Controller core is a configurable single channel direct memory access controller. The DMA IP Core is a Verilog HDL design that can be used in ASIC, Structured ASIC and FPGA designs. The design is intended to be used with AMBA based systems as a controller to transfer data directly from system memory to memory or system memory to peripheral device or IP Core.

Once set up, the DMA controller is primarily an AHB Master component, which initiates data transfers across the AHB bus to/from a peripheral device through the DMA Buffer. The DMA Buffer is a 16x32 FIFO, which is useful for peripheral devices requiring a steady stream of data such as an LCD Controller, Ethernet MAC or other communication device.

The DMA controller contains useful features such incrementing and non-incrementing addressing and link list operation. Linked list support is useful for non-contiguous memory transfer operations.

Multiple DMA controllers can be placed in the AHB System to provide multiple channel DMA control.

Key features

- AHB Master/Slave component DMA Controller

- Single Channel – multiple instantiation

- Memory to Memory. Memory to Peripheral, Peripheral to Memory, Peripheral to Peripheral modes

- Source and destination address descriptors

- Single word and burst transfer requests

- Programmable burst size

- Current address status

- Incrementing and non-incrementing addressing

- Transfer complete interrupt

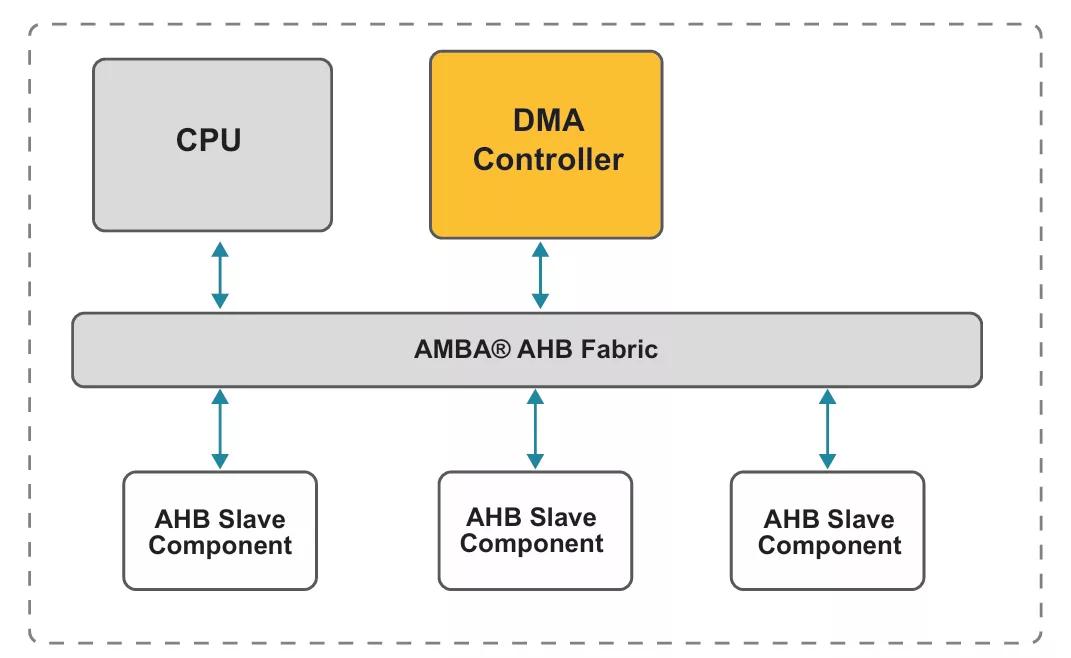

Block Diagram

What’s Included?

- Verilog Source

- Complete Test Environment

- AHB Bus Functional Model

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about DMA IP core

Using peripheral DMA boosts networked 32 bit MCU security and bandwidth

New AXI Scatter-Gather DMA Core Transfers Streaming Data to/from System Memory

Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

Considerations When Architecting Your Next SoC: NoCs with Arteris

Can Your NPU Run DOOM? Chimera Can.

Frequently asked questions about DMA IP

What is AHB Single Channel DMA Controller?

AHB Single Channel DMA Controller is a DMA IP core from Silvaco, Inc. listed on Semi IP Hub.

How should engineers evaluate this DMA?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DMA IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.