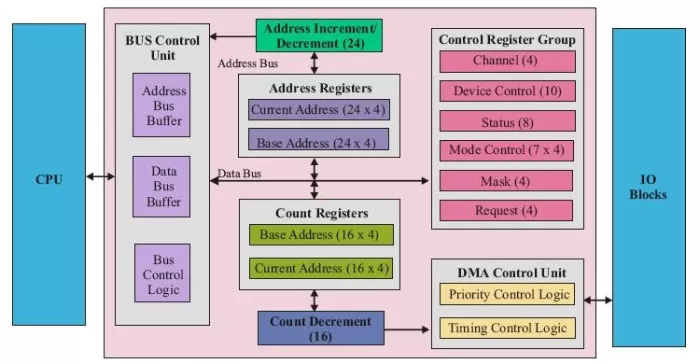

8237 DMA Controller is a peripheral core for microprocessor systems. It controls data transfer between the main memory and the external systems with limited CPU intervention.

8237 DMA Controller

Overview

Key Features

- 24-bit length address register

- 16-bit length count register

- 4 independent DMA channels

- 4 clock / 1 bus cycle

- Byte transfer / word transfer selectable

- Supports three transfer modes (Single, Demand, Block)

- DMA request Maskable on an individual channel basis

- Software DMA request in uPD1037 mode

- Auto initialization function

- Two kinds of channel priority order (Fixed & Rotating)

- Cascading capability

Benefits

- Used to reduce the load of the CPU

- Configurable for ease of use

Block Diagram

Applications

- Core is designed to use with industry standard microprocessors.

Deliverables

- Design Document

- Verilog RTL or Netlist Source code

- Test Bench

- IP User Guide

Technical Specifications

Maturity

Not Applicable

Availability

Available