The 2.5Gb MAC core can support data rates of 1Gbps or 2.5Gbps in LatticeSC/M™ devices. The 2.5Gb MAC transmits and receives data between a host processor and an Ethernet network. The main function of the Ethernet MAC is to ensure that the Media Access rules specified in the 802.3 IEEE standards are met while transmitting and receiving Ethernet frames.

The data received from the GMII interface is first buffered until sufficient data is available to be processed by the Receive MAC (Rx MAC). The Preamble and the Start of Frame Delimiter (SFD) information are then extracted from the incoming frame to determine the start of a valid frame. The Receive MAC checks the address of the received packet and validates whether the frame can be received before transferring it into the FIFO. Only valid frames are transferred into the FIFO. The 2.5Gb MAC however always calculates CRC to check whether the frame was received error-free or not.

2.5Gb Ethernet MAC

Overview

Key Features

- Compliant to IEEE 802.3z standard

- Generic 8-bit host interface

- 8-bit wide internal data path

- Generic transmit and receive FIFO interface

- Full-duplex operation

- Transmit and receive statistics vector

- Programmable Inter Packet Gap (IPG)

- Multicast address filtering

- Supports

- Full-duplex control using PAUSE frames

- VLAN tagged frames

- Automatic re-transmission on collision

- Automatic padding of short frames

- Multicast and Broadcast frames

- Optional FCS transmission and reception

- Optional MII management interface module

- Supports jumbo frames up to 9600 bytes

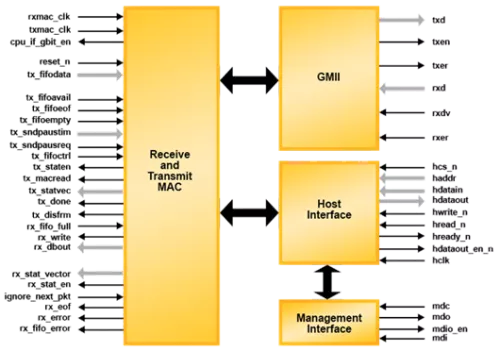

Block Diagram

Technical Specifications

Short description

2.5Gb Ethernet MAC

Vendor

Vendor Name