10-bit successive approximation Analog-to-Digital Converter (ADC) is designed for high-performance applications. Utilizing 28FDSOI technology with process options including 6 Metal (5+1), 8 Metal

(6+2), and 10 Metal (6+2+2), this ADC achieves exceptional performance while maintaining a compact silicon footprint.

With a parallel 10-bit output, this ADC offers a conversion time of 1 µs and a sampling frequency of 1 Msps, making it suitable for applications

requiring fast and accurate analog-to-digital conversion. In terms of performance, the ADC delivers exceptional accuracy with Integral Non-Linearity (INL) of less than ±1 LSB and Differential NonLinearity (DNL)of less than ±0.5 LSB, ensuring precise conversion of analog signals into digital data.

Overall, this ADC offers high-performance analogto-digital conversion in a compact and efficient

package, making it ideal for a wide range of

applications including industrial automation,

medical imaging, and telecommunications.

10bit 1Msps SAR ADC IP Core

Overview

Key Features

- 10-bit Parallel Output.

- Conversion time/Sampling frequency = 1 us/ 1Msps

- CLOCK REQUIREMENT: 2 MHz- 20 MHz

- SUPPLY REQUIREMENT: 1.8 V Analog/0.9 V Digital

- PERFORMANCE PARAMETERS:

- -INL

- a. Typ= +/- 1 LSB

- b. Max= +/- 2 LSB

- -DNL

- c. Typ= +/- 0.5 LSB

- d. Max= +/- 1 LSB

- -EOB

- e. Typ= +/- 3 LSB

- f. Max= +/- 5 LSB

- -EOT

- g. Typ= +/- 3 LSB

- h. Max= +/- 5 LSB

- -ANALOG INPUT FREQUENCY

- i. Typ= 100 KHz

- -SNDR (Fin=100Khz,Fs=1MHz)

- j. Min= 48 dB

- k. Typ= 50 dB

- Process option: 6 Metal (5+1),8 metal (6+2) and 10 Metal (6+2+2)

- TEMPERATURE RANGE: Min= -40, Typ= 25, Max= 125

- Silicon Proven in 28FDSOI

- Production Proven

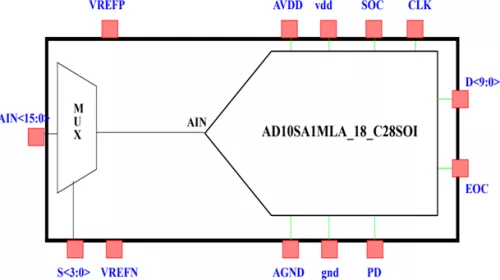

Block Diagram

Deliverables

- Detailed Datasheet

- Verilog behavior model (A) for simulation

- Liberty (db./.lib) for synthesis, STA, and equivalence checking

- CTL / CTLDB for DFT

- SPF (Standard Test Interface Language (STIL Procedure File) for ATPG

- LEF for APR

- CDL for LVS connection

Technical Specifications

Short description

10bit 1Msps SAR ADC IP Core

Vendor

Vendor Name

Maturity

In Production

Availability

Immediately