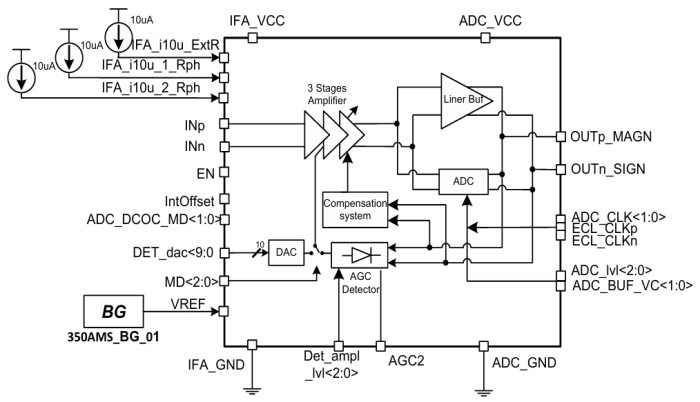

IFA consists of 3 stages amplifier with tunable gain, AGC system, linear buffer for analog output and an analog-digital converter (ADC) for 2-bits digital output and a detector of output level.

The amplifier has differential inputs and outputs. Gain is sequentially reduced from the last stage to the first stage. This method allows to keep a low noise figure in wide gain range.

In the analog output mode the circuit controls the gain so that the magnitude of the differential output signal. The signal level is set through Det_ampl_lvl<2:0>.

Digital output with AGC for analog signal mode operates similarly to the previous mode.

AGC operates in an automatic control mode of digital detector threshold for digital signal (MAGN). Threshold and gain are set by the DAC code. Digital output level is set 1.8V, 2.4V, 2.7V, ADC_VCC.

DC offset compensation system operates both at an amplifier output signal and at a buffer output signal.

1 to 30 MHz Intermediate-Frequency Amplifier with Wide Gain Range

Overview

Key Features

- AMS SiGe BiCMOS 0.35um

- Wide gain range (0…60 dB)

- Low group delay time ripple vs. frequency and gain

- Digital and analog output modes

- Built-in AGC system and DCOC

Block Diagram

Applications

- Navigation systems

- Receivers

- Transceivers

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

1 to 30 MHz Intermediate-Frequency Amplifier with Wide Gain Range

Vendor

Vendor Name

Foundry, Node

AMS SiGe BiCMOS 0.35um

Maturity

Silicon proven

Availability

Now

Related IPs

- Intermediate frequency amplifier with wide gain range

- 64 dB Intermediate frequency amplifier with wide gain range

- 900MHz, 2140MHz & 2700 MHz, 1 watt wide band Power Amplifier

- 0.035... 100 MHz intermediate-frequency amplifier

- 900MHz, 2140MHz & 2700 MHz, 2 watt wide band Power Amplifier

- 5 to 20 MHz Intermediate-frequency amplifier