Paving the way for the next generation of audio codec for True Wireless Stereo (TWS) applications - PART 5 : Cutting time to market in a safe and timely manner

By Hai YU, Clément MOULIN (Dolphin Design)

In this fifth and last part of Paving the way for the next generation audio codec for True Wireless Stereo (TWS) applications whitepaper, a hastened but safe and improved design flow by Dolphin Design will be discussed.

Straightforward and smooth IP integration, time-to-market

For the consumer market of TWS chips, the time-to-market window is quite tight. The consumer business is all about finding popular trends and being able to ride a short-lived wave with a successful product. Therefore, the performance, power and manufacturing challenges are compounded by the need to enter the market quickly. Last, but never least, is cost. Consumer margins are always tight, and they get tighter as a product category or feature set matures, and other vendors enter the market.

However, with audio-oriented application like TWS, the integration of an audio codec IP is always time consuming and painful since every single unintentional design error will cause the audio codec to either malfunction or have degraded performance.

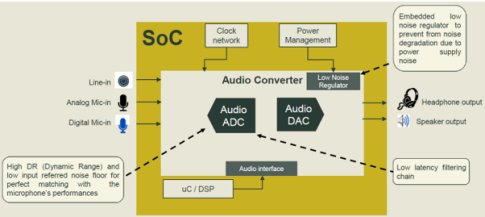

Fig. 1: Dolphin’s audio codec global view

Consequently, to ease audio codec IP integration in a smooth manner, the precautions that are taken into consideration within the IP as stated previously, such as; the embedded low-noise voltage regulator against power supply noises, the AIAS interface used to tolerate the clock jitters, and a rich set of user interfaces, etc. are complemented by a complete set of fully verified deliverables.

The complete documentation set (datasheet, user manual, application note, checklists, reference application schematic, reference layout, etc.) provides detailed descriptions and integration guidelines that allow the SoC integrator to have a smooth IP integration. Additionally, a set of milestone checklists are put into place during each SoC integration step, and the SoC integrator will be accompanied by an experienced application engineer during the checklist review to ensure that there are no issues during the IP integration phase, printed circuit board design phase and chip industrial test phase.

There are rigorous tolerance templates both for the main clock and the power supply to ensure the best-of-class audio quality. The master clock Jitter Tolerance Template (JT2) will allow the SoC integrator to easily select the appropriate clock source (PLL, DLL, …) and avoid any performance degradation from the clock jitter perspective. Similarly, the Power Supply Noise Tolerance Template (PSNT2) that describes the noise profile will allow the SoC integrator to select the correct voltage regulator to power the audio codec IP.

SoC integration is simplified by the rich set of plug and play data and control interfaces embedded in the audio codec IP. The standardized user interfaces, such as AMBA bus interface (AHB-Lite, APB, …), I2S, I2C and parallel data interface of the mainstream MCU or DSP are supported, which provide much more flexibility during SoC integration.

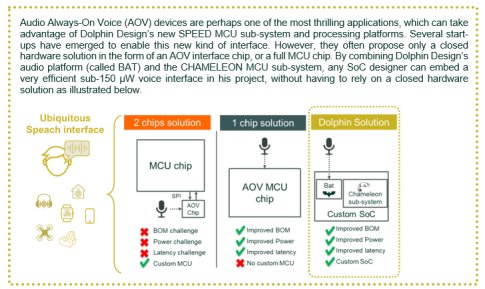

Fig. 2: Dolphin Design’s solution for audio AOV devices

SPIDER Platform At the edge of data processing

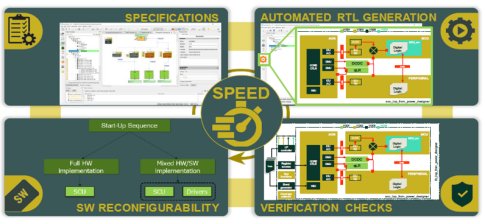

Fig. 3: SPIDER platform at a glance edge of data

SPEED Platform At the edge of data processing

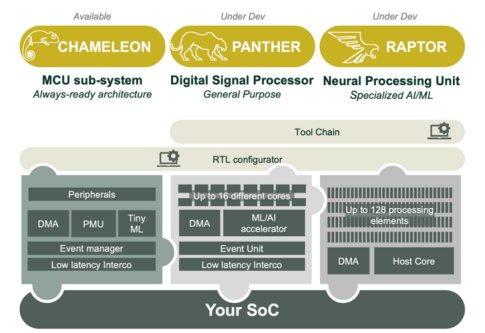

Dolphin Design has been working very intensively these last two years to extend its offer in ultra-efficient IPs and will soon release the System Platforms for Energy Efficient Design (a.k.a. SPEED), which integrates all the good practices mentioned above. The cornerstone of the SPEED platform is the CHAMELEON MCU subsystem, a flexible and pre-verified event-based MCU subsystem platform embedding several standard peripherals, an autonomous DMA, a fined-grained power management unit, a tiny ML accelerator, a low latency interconnect, and an event manager. It allows fast & efficient CPU-less data collection & filtering, enabling extremely low power consumption in both deep sleep and active modes.

CHAMELEON can be further enhanced by 2 processing platforms.

PANTHER is a highly configurable DSP platform based on up to 16 processing elements and an ML/AI accelerator. The platform embeds an event manager as well as a low latency interconnect to maximize the energy efficiency. The platform will come with an RTL configurator and a tool chain. PANTHER enables more than 7 GOPS computing performance and an efficiency of 120 GOPS/W (@2.2 GOPS) in 40 nm LP technology.

RAPTOR is a second companion processing unit targeting neural networks inference and audio/vision processing algorithm which improves the operation/power ratio even further. It includes a host core, a DMA, and up to 128 processing elements. RAPTOR enables more than 60 GOPS computing performance and an efficiency of 2200 GOPS/W (@16 GOPS) in 28 nm FD-SOI technology.

Fig. 4: Dolphin Design MCU sub-system and processing platforms

ABOUT THE AUTHORS

Hai YU received his PhD in Nano and Micro Electrical Engineering in 2011 from TIMA laboratory, Grenoble Alpes University for his work on low-cost highly efficient fault tolerant processor design for mitigating the reliability issues in nanometric technologies. Hai joined Dolphin Design in 2012 and is currently working as a Lead Application Engineer, focusing on Audio & Processing IPs platforms.

Clément MOULIN graduated from ENSEEIHT Toulouse in electronic and signal processing in 2006. After 8 year of leading hardware development in NFC domain, Clément joined Dolphin Design in 2020 and is currently working as an Application Engineer, focusing on Audio & Processing IPs platforms.

Related Semiconductor IP

- Verification IP for I3C/I2C

- Verification IP for SATA

- Verification IP for SAS

- Verification IP for DisplayPort/eDP/DSC/DPI

- Verification IP for HDMI

Related White Papers

- Paving the way for the next generation audio codec for True Wireless Stereo (TWS) applications - PART 2 : Increasing play time

- Paving the way for the next generation audio codec for the True Wireless Stereo (TWS) applications - PART 1 : TWS challenges explained

- Paving the way for the next generation audio codec for True Wireless Stereo (TWS) applications - PART 3 : Optimizing latency key factor

- Paving the way for the next generation audio codec for TRUE Wireless Stereo (TWS) applications - PART 4 : Achieving the ultimate audio experience

Latest White Papers

- Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

- Automating NoC Design to Tackle Rising SoC Complexity

- Memory Prefetching Evaluation of Scientific Applications on a Modern HPC Arm-Based Processor

- Nine Compelling Reasons Why Menta eFPGA Is Essential for Achieving True Crypto Agility in Your ASIC or SoC

- CSR Management: Life Beyond Spreadsheets