digital ADC IP

Filter

Compare

362

IP

from

62

vendors

(1

-

10)

-

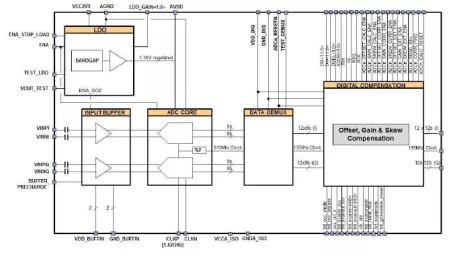

Dual core I & Q Analog to Digital Converter

- Maturity MAT05

- 9-bits DUAL-CORE I & Q SAR ADC

- Up to 1.62Gsps Sampling Rate

- Analog power supply for Input Buffer: from 1.7V to 2.75V (GO2 domain)

-

6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

- 6-bit resolution

- 12 GSPS sampling rate

- 10 GHz Input Bandwidth

- 13 mW Power

-

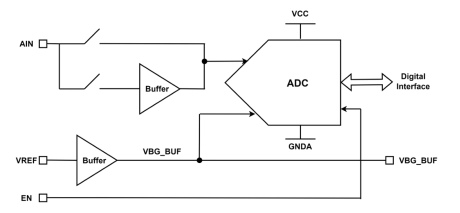

10-bit SAR ADC - XFAB XT018

- The TS_ADC_10b_X8 is a 10-bit capacitive successive approximation register (SAR) Analog-to-Digital converter (ADC).

- It operates with a 3.3 V analog power supply, a 1.8 V digital power supply, and an external voltage reference.

- The ADC converts single-ended input voltages and requires no external S/H circuit.

-

12-bit, 400 MSPS SAR ADC - TSMC 12nm FFC

- 12-bit Resolution

- 400 MSPS Sampling Rate

- 1 GHz Input Bandwidth

- Differential voltage input

- 4.2 mW Power

-

10-bit Pipeline ADC - Tower 180 nm

- 10-bit resolution

- 25 MSPS sampling rate

- 6 mW power

- 25 MHz Input Bandwidth

-

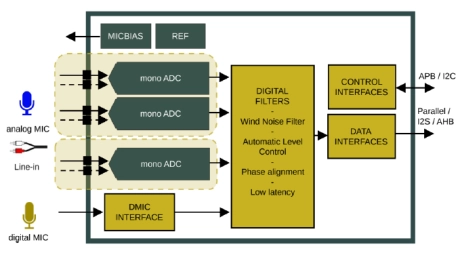

106dB, 24-bit audio three-channels ADC in TSMC 40uLP

- tADC106-SW1-LR.01_TSMC_40_uLP is a mixed (analog and digital) Virtual Component (ViC) in TSMC 40uLP containing a three-channel ADC and additional functions offering an ideal mixed signal front end for low power and high quality audio applications.

-

24-bit Cap-less ADC with 101 dB SNR, offering low power consumption and low latency, supporting 1 channel (mono) in TSMC 12FFC+

- mADC101-SW3-FF.01 is a mixed-signal (analog and digital) virtual component in TSMC 12FFC+ that includes a single mono ADCs and additional functions, making it an ideal front-end for low power, fast wake-up, and high-quality audio applications.

- It also features ultra-low latency capability for ANC applications.

-

10Bit 25MHz sigma-delta ADC for VT sensor on SMIC 40nm

- The present IP is a single-ended 10-bit Sigma-Delta (SD) analog-to-digital converter

- This ADC operates with one 1.1V power supplies with low power consumption

- The 1.1V digital power supply is employed for easy integration with 1.1V digital signal processors and macro processors.

-

13-bit, 80 MSPS ADC - TSMC 65nm

- The A13B80M is a low-power, high-speed analog to digital converter (ADC) intellectual property (IP) design block.

- It is a hybrid-SAR ADC, with 13-bit resolution and a sampling speed of 80 megasamples per second (MSPS).

-

12-bit, 9.2 GSPS Pipeline ADC - GlobalFoundries 22nm

- The A12B9G is a low-power, high-speed analog to digital converter (ADC) intellectual property (IP) design block.

- It is a time-interleaved successive approximation register (SAR) ADC, with 12-bit resolution, and a sampling speed of 9 giga samples per second (GSPS).