cryptographic IP

Filter

Compare

263

IP

from

47

vendors

(1

-

10)

-

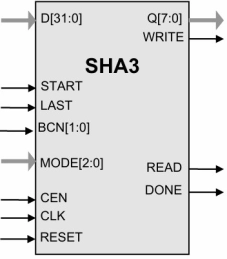

SHA3 Cryptographic Hash Cores

- Completely self-contained; does not require external memory

- SHA3-224, SHA3-256, SHA3-384, and SHA3-512 support SHA-3 algorithms per FIPS 202.

- SHAKE128 / SHAKE256 XOF support is included.

- Flow-through design; flexible data bus width

-

Cryptographic engine using the DES, Triple-DES or AES

- The cryptographic processor (CRYP) can be used both to encrypt and decrypt data using the DES, Triple-DES, AES or SM4 algorithms.

-

Asymmetric cryptographic accelerator

- The ACrypto Engine is an asymmetric cryptographic accelerator suitable for embedded application.

- It provides capability for basic arithmetic and frequently used operations. Along with driver, it is flexible to support popular upperlayer applications.

-

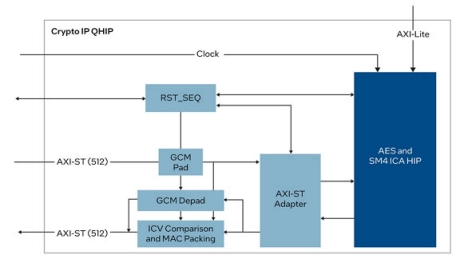

Symmetric Cryptographic Intel® FPGA IP

- The Symmetric Cryptographic Intel® FPGA IP is a hard IP core implementing AES and SM4 encryption and decryption

- Typically, the AES and SM4 standards are used to protect the confidentiality of network data in 5G, data center, and IoT applications, but can be used to secure any high-speed data in transit

- Additionally, the XTS profile can be used in data storage applications.

-

Cryptographic Cores IP

- The Cryptographic Cores IP portfolio delivers secure, high-performance implementations of symmetric, asymmetric, and post-quantum algorithms.

- Designed for low-area, low-latency operation, the silicon-proven cores help SoC designers and embedded teams build trusted, efficient devices for IoT, automotive, medical, and industrial markets.

-

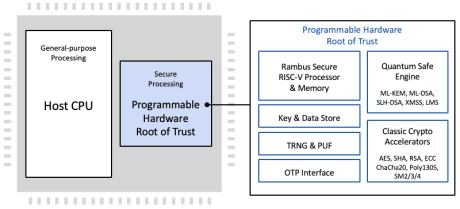

Programmable Root of Trust with Quantum Safe Cryptography acceleration, DPA-resistant & FIA-protected cryptographic accelerators and Caliptra RoTM

- The CryptoManager RT-6xx v3 Root of Trust family from Rambus is the latest generation of fully programmable FIPS 140-3 compliant hardware security cores offering Quantum Safe security by design for data center and other highly secure applications.

- Device and system architects face a growing array of security threats, including the threat of quantum computers. Across applications, one constant is the need for a hardware Root of Trust-based security implementation.

-

Cryptographic co-processor for lightweight cryptography

- Support AES-XTS mode — IEEE Std 1619-2007 standard compliance

- Support 128 and 256-bit key size

- Random memory block access support

-

HMAC-SHA256 cryptographic accelerator

- Hardware Root of Trust

- Widely used password hash algorithm

- Security Critical HTTP, SSL, TLS

- Key storage in Private memory

-

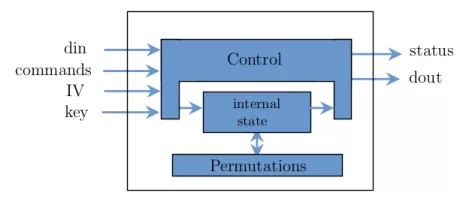

Ascon, A Lightweight Cryptographic Suite for AEAD and Hashing

- Small Resource Requirements

- Versatile Algorithm Support

- Secure Architecture

-

Advanced Encryption Standard Cryptographic Co-Processor

- The DAES IP Core is a high-performance AES hardware accelerator designed to execute Advanced Encryption Standard (AES) operations with exceptional speed, reliability, and energy efficiency.

- Optimized for embedded systems, SoCs, FPGA designs, and other security-critical applications, the DAES IP Core significantly offloads computationally intensive AES tasks from the main processor, enhancing both system performance and power efficiency.