ZigBee 3.0 IP

Filter

Compare

5

IP

from

4

vendors

(1

-

5)

-

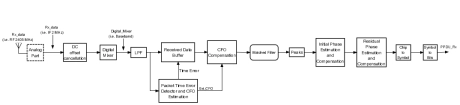

Zigbee Transceiver PHY

- Low power transceiver PHY IP for ZigBee applications, compliant with IEEE 802.15.4 standard.

- Efficient demodulator with frame synchronization and frequency offset compensation

- Supports 2 MHz IF input (reconfigurable on request)

- Offset-QPSK (OQPSK)

-

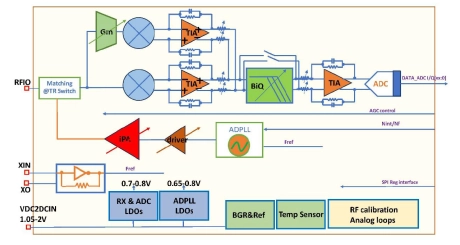

Bluetooth Low Energy 6.0 Scalable RF IP

- The SB1001 Scalable RF Transceiver IP is designed to maximise Performance per μW across the full range of BLE applications, enabling active Receiver power consumption as low as 3mW for medical devices, whilst delivering up to +10dBm for Transmit when needed for industrial applications.

- It is optimised for applications such as BLE, 802.15.4 (Zigbee, Matter) and proprietary standards operating at 2.4GHz.

- It is optimised for applications such as BLE, 802.15.4 (Zigbee, Matter) and proprietary standards operating at 2.4GHz.

-

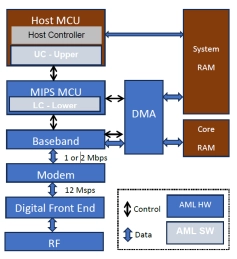

Bluetooth Low Energy Subsystem IP

- The BLE v6.0 Subsystem IP consists of an integrated Controller and Modem paired to a proprietary RF on T22 ULL.

- It is ideally suited to ASIC developers or fabless semiconductor companies who want to add BLE functionality without the hassle of dealing with multiple IP vendors or design groups.

-

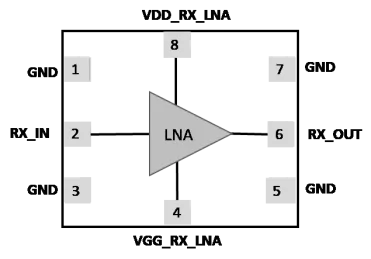

Single stage low noise amplifier from 2-6 GHz with flat gain, low Noise Figure, high isolation, stability.

- RF Frequency: 2-6 GHz

- Noise Figure of 1.4 dB

- Small Signal Gain of 14.6 dB

- OP1dB of 18.8 dBm

-

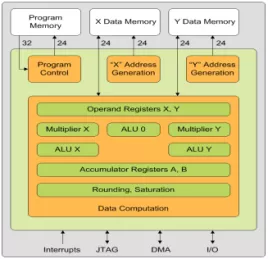

Ultra low power C-programmable Baseband Signal Processor core

- Ultra low power consumption

- Highly optimizing C-compiler software toolkit

- Minimal core size (65k gates), excluding debug interface (6k gates)

- Small memory footprint