ZeroPoint IP

Filter

Compare

8

IP

from

2

vendors

(1

-

8)

-

High performance and low latency hardware accelerated zram/zswap at unmatched power efficiency

- Compression ratio: 2-4x across diverse data sets

- Compression throughput: 8GB/s

- Decompression throughput: 10.5GB/s

-

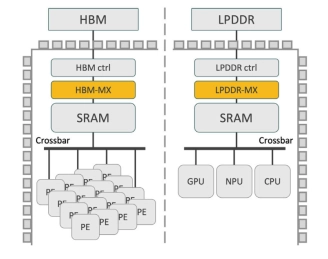

High-Performance Memory Expansion IP for AI Accelerators

- Expand Effective HBM Capacity by up to 50%

- Enhance AI Accelerator Throughput

- Boost Effective HBM Bandwidth

- Integrated Address Translation and memory management:

-

NVMe expansion

- Turn key solution: compression, compaction, memory management

- Transparent addressing to operating system and applications

- Operates on page granularity to enable high compression performance

-

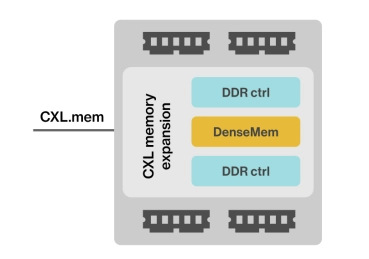

CXL memory expansion

- Turn key solution: compression, compaction, memory management

- Automatic compressed memory tier

- Multi-instance support to match interface throughput

- Cache line granularity decompression for highest read performance (proprietary algorithm)

-

On-chip memory expansion

- On-the-fly compression / decompression of cache lines

- Optional secureTraining on metadata capability

-

Up to 50% main memory bandwidth acceleration

- Bandwidth acceleration: 25-50%

- Performance acceleration: 10-25%

- Compression ratio: 2-3x across diverse data sets

-

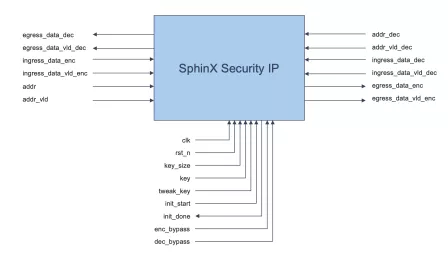

AES-XTS encryption/decryption IP

- High Performance and Low Latency industry standard encryption / decryption

- Independent non-blocking encryption and decryption channels

- 128b and 256b keys supported

-

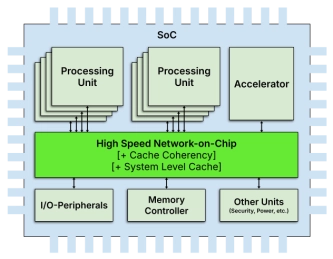

Network-on-Chip (NoC)

- InfiniNoC is a highly customizable Network-on-Chip (NoC) from InfiniNode Technologies, designed to provide a scalable, high-performance communication backbone for next-generation SoCs.

- It enables seamless integration of diverse IP blocks while delivering the flexibility, scalability, and performance required to accelerate complex chip development.

- The architecture supports high bandwidth and low latency alongside energy-efficient data movement, and it can be customized to match specific use cases and requirements.