Vision IP

Filter

Compare

103

IP

from

34

vendors

(1

-

10)

-

-

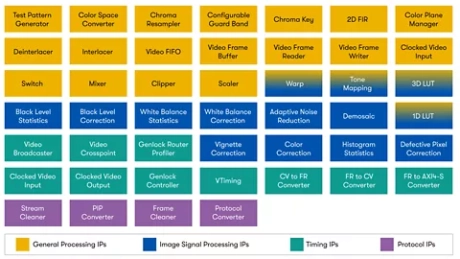

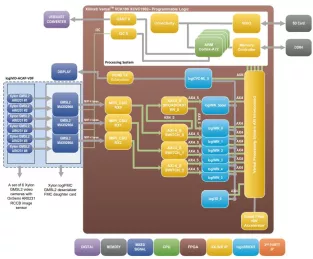

Video and Vision Processing Suite

- The Intel® FPGA Video and Vision Processing Suite is a collection of next-generation Intel® FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel® FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, industrial inspections and robotics, smart city/retail and consumer.

-

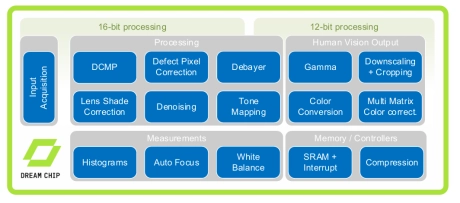

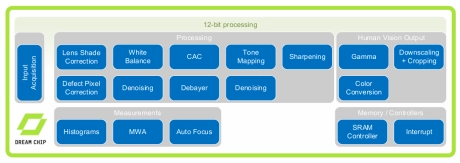

Real-time Pixel Processor for Vision applications

- The W Series provides configurable input and output data widths.

- It supports input image frames with 8 to 16-bit amplitude resolutions, while it can output tone-mapped frames with 12 bits per pixel.

- The W Series are ISPs which are optimized for area while getting the best image quality.

-

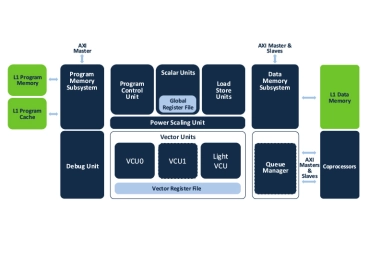

Tensilica Vision P1 DSP

- 256/128b Load/Store capabilities

- 128 8-bit MAC

- 8/16/32-bit fixed-point processing

- Single-precision (FP32) and half-precision (FP16) floating-point processing

-

Tensilica Vision P6 DSP

- 1024/512b Load/Store capabilities

- 256 8-bit MAC

- 8/16/32-bit fixed-point processing

- Single-precision (FP32) and half-precision (FP16) floating-point processing

-

Tensilica Vision Q8 DSP

- 2048/1024b Load/Store capabilities

- 1024 8-bit MAC: 2X MAC capability versus Vision Q7 DSP

- 8/16/32-bit fixed-point processing

- Double-precision (FP64), single-precision (FP32), and half-precision (FP16) floating-point processing

-

Video Design Framework for Multi-camera Vision Applications

- Complete video design framework for embedded multi-camera vision applications

-

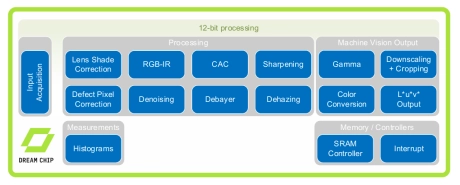

Real-time Pixel Processor for Vision applications

- The H Series provides configurable input and output data widths. It accepts YCbCr or RAW input data and supports input image frames with 8, 10 and 12-bit amplitude resolutions.

- The H1 Series are ISPs which are optimized for area while getting the best image quality.

- Options to extend the pipeline with a Machine Vision output or configuring the line size to further optimize area are possible.

-

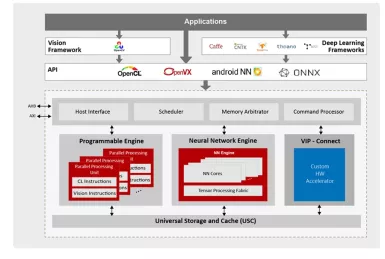

NPU IP for AI Vision and AI Voice

- 128-bit vector processing unit (shader + ext)

- OpenCL 3.0 shader instruction set

- Enhanced vision instruction set (EVIS)

- INT 8/16/32b, Float 16/32b

-

Vision AI DSP

- Ceva-SensPro is a family of DSP cores architected to combine vision, Radar, and AI processing in a single architecture.

- The silicon-proven cores provide scalable performance to cover a wide range of applications that combine vision processing, Radar/LiDAR processing, and AI inferencing to interpret their surroundings. These include automotive, robotics, surveillance, AR/VR, mobile devices, and smart homes.