Universal TV Encoder IP

Filter

Compare

429

IP

from

54

vendors

(1

-

10)

-

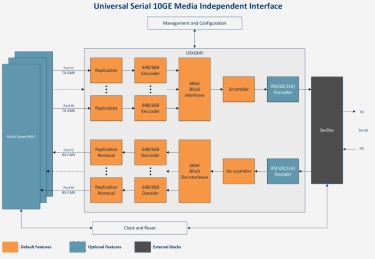

Universal Serial 10GE Media Independent Interface (USXGMII)

- The USXGMII PCS IP provides the logic required to integrate a USXGMII-M IP into any system on chip (SoC).

- Link speeds of 5G, 10G, or 20G are supported. Compliant with the Cisco Universal SXGMII Interface for multiple Multi-Gigabit Copper Network Ports and IEEE 802.3 Clause 49 standards, the PCS IP has several optional features to customize the physical coding sublayer (PCS) for the specific needs of any application.

-

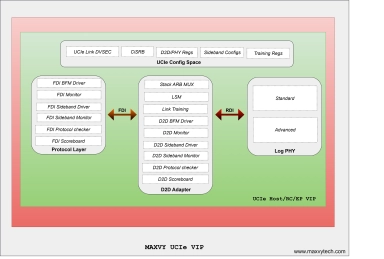

Universal Chiplet Interconnect Express(UCIe) VIP

- The UCIe VIP , a state-of-the-art solution that offers a comprehensive set of features and capabilities to ensure the quality and performance of your UCIe designs

- The UCIe VIP is fully compliant with UCIe Specification version 1.0 and supports all the layers of the UCIe stack, such as FDI, RDI, LogPHY, PCIe, and CXL protocols

- The UCIe VIP is also very user-friendly and flexible, with simple APIs, easy integrations, and configurable parameters

-

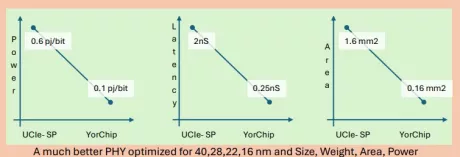

UCIe and BOW Universal PHY

- Novel Redundancy for Hi-Rel,

- Support for 16&18-bit wide data,

- Support Synchronous Operation,

- Supports Advanced packaging,

-

Universal Synchnonous/Asynchronous Receiver Transmitter (UART/USART)

- Dolphin Technology provides Universal Synchnonous/Asynchronous Receiver Transmitter (UART/USART) IP which allows the communication of serial character streams between an embedded system and an external device.

- This communication is done by reading and writing control and data registers.

- The core implements the RS-232 protocol timing and provides ability to adjust baud rate, parity, stop, and data bits.

-

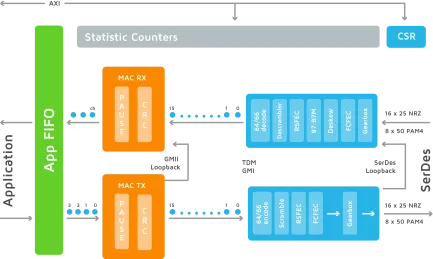

Multi-channel, multi-speed Ethernet universal media access control (MAC) and physical coding sublayer IP (UMAC)

- Programmable application-side FIFO sizes (or complete bypass ) on TX, RX or both for easy integration with application logic

- Packing and unpacking logic for application to internal data path matching

- Supports line rate with minimum IFG

- Memory-based statistics counter implementation for Area/gate savings

-

0.6G - 12.5G Universal SerDes

- 0.6Gbps to 12.5Gbps universal SERDES IP

- Support full, 1/2, 1/4 and 1/8 data rate mode

- Support up to 12 TX/RX data lanes with shared PMU

- Fractional PLL for wide data rate range selection

-

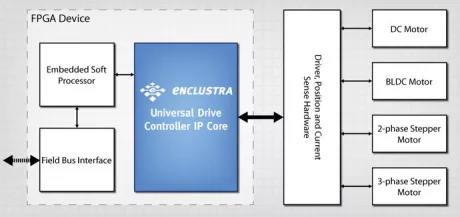

Universal Drive Controller

- Evaluation Kit available

- Support for DC, BLDC, 2- and 3-phase stepper motors

- Support for encoders and resolvers

-

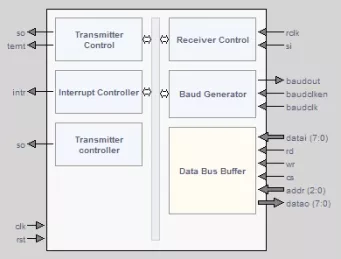

High Speed UART IP core - Universal Aysynchronous Receiver / Transmitter

- Software compatible with SCC2698 UART

- Configuration capability

- 8 full-duplex independent asynchronous receiver/transmitters

- 3 character FIFOs for each receiver channel

-

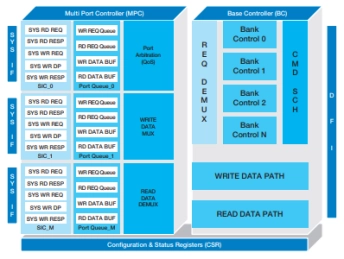

Universal Multi-port Memory Controller for RLDRAM2/3, DDR5/4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- The UMMC (Universal Multi-port Memory Controller for RLDRAM2/3, DDR5/4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2) is a highly flexible and configurable design that supports RLDRAM2, RLDRAM3 and JEDEC compliant DDR5, DDR4 3DS, DDR4, DDR3, LPDDR3, LPDDR3 and LPDDR2 memories.

- It is targeted for high bandwidth access and low power consumption such as next-generation mobile, networking and consumer applications. The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities

-

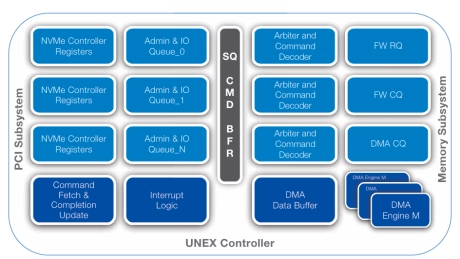

Universal NVM Express Controller (UNEX)

- The Universal NVM Express Controller (UNEX) is highly flexible and configurable design targeted for both Enterprise and client class solutions that unlock the current and future potential of PCIe-based SSDs.

- The UNEX controller core efficiently supports multi-core architectures ensuring thread(s) may run on each core with their own queue and interrupt without any locks required.

- It provides support for end-to-end data protection, security and encryption as well as robust error reporting and management capabilities.