USB3 IP

Filter

Compare

118

IP

from

25

vendors

(1

-

10)

-

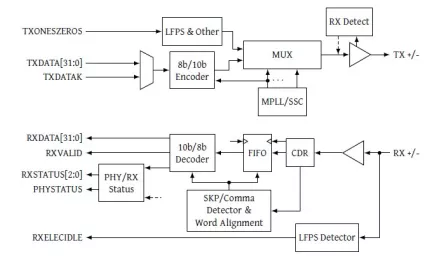

USB 3.0 PHY

- Standard PHY interface (PIPE) enables multiple IP sources for USB 3.0 Link Layer

- Supports 5.0 GT=s serial data transmission rate

- Supports 16- or 32-bit parallel interface

- Supports PCLK as PHY output

-

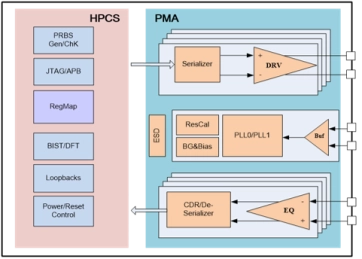

USB3.1 transceiver IP with PMA and PCS layer

- Data rate for Gen 1 physical layer is 5Gbps

- Data rate for Gen 2 physical layer is 10Gbps

- 4 Channel per Quad

- Shared high performance LC tank PLL

-

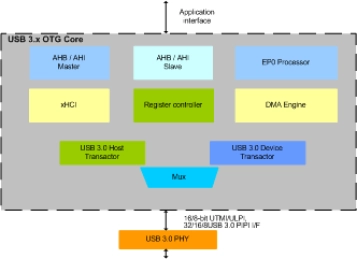

USB3.x OTG IIP

- USB 3.0/3.1/3.2 Common support

- Compliant with USB 3.0/3.1/3.2 specification

- Supports Superspeed USB 3.0, SuperSpeedPlus 3.1, 3.2

- Configurable number of Configurations, Interfaces, Alternative Interfaces and Endpoints

-

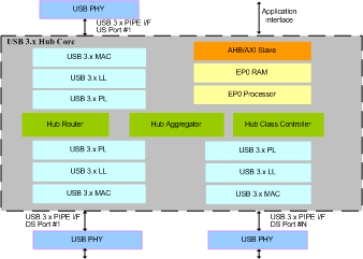

USB3.x HUB IIP

- USB 3.0/3.1/3.2 Common support

- Compliant with USB 3.0/3.1/3.2 specification

- Supports Superspeed USB 3.0, SuperSpeedPlus 3.1, 3.2

- Configurable number of Configurations, Interfaces, Alternative Interfaces and Endpoints

-

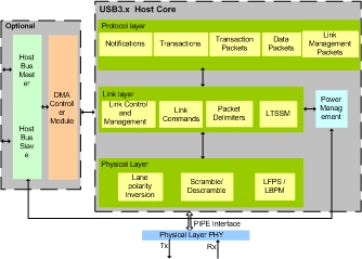

USB3.x HOST IIP

- USB 3.0/3.1/3.2 Common support

- Compliant with USB 3.0/3.1/3.2 specification

- Supports Superspeed USB 3.0, SuperSpeedPlus 3.1, 3.2 and 3.0 OTG

- Configurable number of Configurations, Interfaces, Alternative Interfaces and Endpoints

-

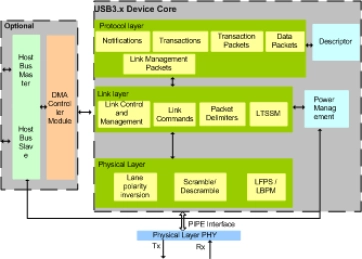

USB3.x DEVICE IIP

- USB 3.0/3.1/3.2 Common support

- Compliant with USB 3.0/3.1/3.2 specification

- Supports Superspeed USB 3.0, SuperSpeedPlus 3.1, 3.2

- Configurable number of Configurations, Interfaces, Alternative Interfaces and Endpoints

-

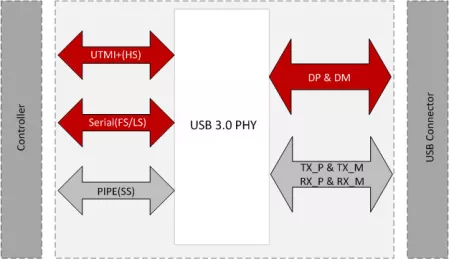

USB3.0 PHY

- Silicon proven in 22, 28, Global Foundries and Samsung

- Spread Spectrum clock (SSC) and data scrambling to minimize EMI

- Supports 16-bit 250-MHz , and 32-bit 125M PIPE interface

- Multiple loopback and compliance test modes

-

USB3.0 PHY on GF22FDX and Samsung 28nm FDSOI

- The USB3.0 PHY IP is designed according to the USB 3.0, USB2.0 Specification.

- It supports the USB3.0 5Gbps Super-Speed mode and backward compatibles with the USB2.0 480Mbps High-Speed, 12Mbps Full-Speed, and 1.5Mbps Low-Speed modes

- The USB 3.0 PHY interface complies with PHY Interface for PCI Express and USB3.0 Architectures specification (PIPE 3.0) and the USB2.0 PHY interface complies with the UTMI v1.05 specification.

-

Samsung 28nm FDSOI USB3.0 and PCIE2 combo PHY

- USB3.0 Super-Speed: Universal Serial Bus 3.0 Specification, Revision 1.0

- PCI Express: PCI Express Base Specification, Revision 2.0

-

GLOBALFOUNDARIES 22nm FDSOI USB3.0 Dual Role PHY/OTG PHY

- Supports 32-bit 125M and 16-bit 250M PIPE interface

- 5-Gbps Super-Speed data transmission rate through 3-m USB3.0 cable

- PIPE 3-compliant Super-Speed USB 3.0 Transceiver interface

- Supports Super-Speed power management modes: U0, U1, U2 and U3