Sarnoff IP

Filter

Compare

7

IP

from

4

vendors

(1

-

7)

-

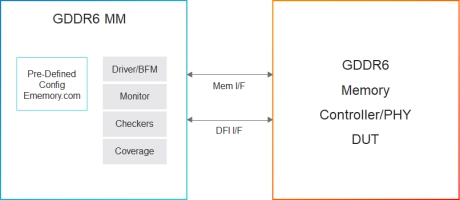

Simulation VIP for GDDR6

- Speed

- Supports up to 16Gbps with current vendor datasheets

- Device Density

- Supports a wide range of device densities from 8Gb to 32Gb

-

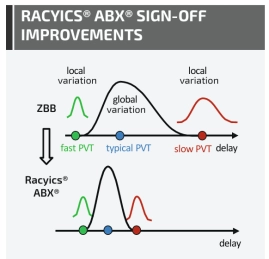

Single Rail SRAM GLOBALFOUNDRIES 22FDX

- Ultra-low voltage logic designs using adaptive body biasing demand dense SRAM solutions which fully integrate in the ABB aware implementation and sign-off flow of the Racyics® ABX Platform solution.

- The Racyics® Single Rail SRAM supports ultra-low voltage operation down to 0.55 V where logic designs with Minimum-Energy-Point are implemented.

-

Standard Cell Libraries - GLOBALFOUNDRIES 22FDX

- Body biasing is a disruptive 22FDX® feature which enables the adaption of transistor threshold voltages after production during device operation.

- Racyics® dense 9T logic standard cells libraries and low power 8T standard cell libraries are fully enabled for the adaptive body biasingaware implementation and sign-off flow of the Racyics® ABX® Platform solution.

-

Dual Rail SRAM Globalfoundries 22FDX

- Single port SRAM compiler based on P124 bitcell with Dual-supply-rail architecture

- Bitcell array supply voltage 0.8V and ULV core interface down to 0.4V enabled with Racyics' ABB

-

SMIC 0.18µm 1.8v/3.3v Power Switch

- Process: SMIC 0.18µm 1.8v/3.3v Logic process

- Operating current: up to 20mA

- Voltage drop: less than 20mV @ 20mA

- Turn-on latency time is less than 100ns

-

12-bit 1Msps Very low power SAR ADC silicon proven in 28nm

- • 12-bit SAR ADC up-to 1MS/s conversion rate.

- • Zero DC power

- • Single-ended/ Differential input

- • 4-input channels

-

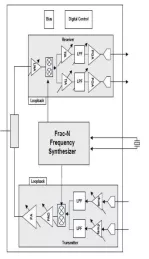

Wi-Fi 802.11 ax/Wi-Fi 6 /Bluetooth LE v5.4/15.4-2.4GHz RF Transceiver IP for IOT Application in TSMC22 ULL

- Metal Layer- 1P7M, 4X1Z1U

- BW support for 20/ 40MHz

- Supports 256 QAM (quadrature amplitude modulation)

- Max Tx output power: +20dBm