RISC-V Microprocessor IP

Filter

Compare

18

IP

from

4

vendors

(1

-

10)

-

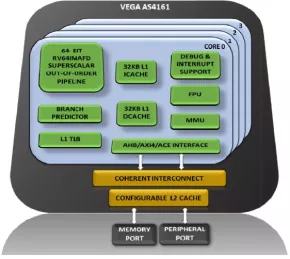

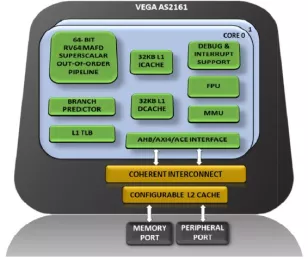

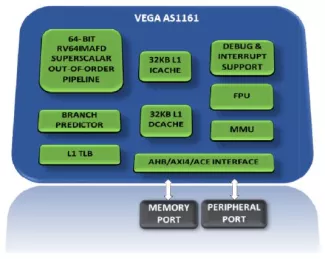

64-bit High performance Quad Core RISC-V Microprocessor

- RISC-V 64G (RV64IMAFD) ISA

- 13-16 stage out-of-order pipeline implementation

- Advanced branch predictor: BTB, BHT, RAS

-

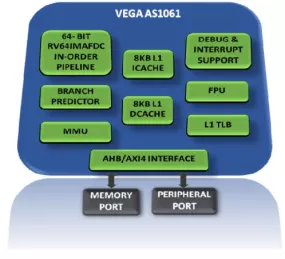

64-bit RISC-V Single Core Microprocessor

- RISC-V 64G (RV64IMAFD) ISA

- 6 stage in-order pipeline implementation

- Advanced branch predictor: BTB, BHT, RAS

- Harvard architecture

-

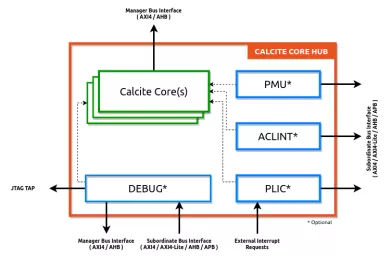

32b/64b RISC-V 5-stage, scalar, in-order, Application Processor. Linux and multi-core capable. Maps upto ARM A-35. Optimal PPA.

- 32/64 Bit RISC-V core

- 5-stage pipeline

- In-order, Single issue

- Multicore Capable (up to 8 cores)

-

32b/64b RISC-V 2-stage, scalar, in-order, Embedded Processor. RTOS and multi-core capable. Maps upto ARM M-4F. Optimal PPA.

- 32-bit RISC-V core

- 2-stage pipeline

- Available in many versions: RV32I[M][C][F][B][P][U]

- 32/16 general purpose registers

-

64-bit High performance Dual Core Microprocessor

- RISC-V 64G (RV64IMAFD) ISA

- 13-16 stage out-of-order pipeline implementation

- Advanced branch predictor: BTB, BHT, RAS

- Harvard architecture

-

64-bit High performance Single Core Microprocessor

- RISC-V 64G (RV64IMAFD) ISA

- 13-16 stage out-of-order pipeline implementation

- Advanced branch predictor: BTB, BHT, RAS

- Harvard architecture

-

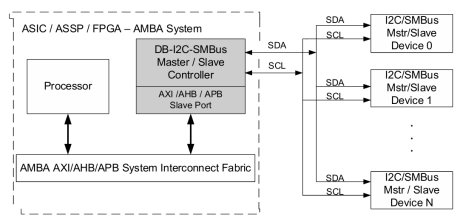

I2C/SMBus Controller IP – Master / Slave, Parameterized FIFO, AXI/AHB/APB/Avalon Buses, SMBus Protocol

- The DB-I2C-SMBus-MS-AMBA Controller IP Core is an I2C/SMBus Master/Slave Controller, interfacing a microprocessor via the AMBA AXI, AHB, or APB Bus to an I2C/SMBus Interconnect. Both I2C and SMBus protocols are supported.

- The System Management Bus (SMBus) is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant SMBus devices, typically with a microprocessor behind the master controller and one or more slave devices.

-

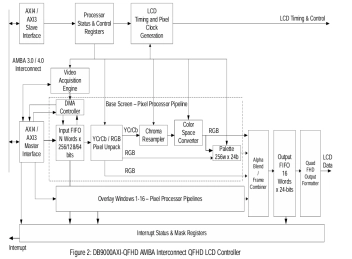

Display Controller – Ultra HD LCD / OLED Panels (AXI4/AXI Bus)

- The DB9000AXI4-UHD LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to an 4K/8K TFT LCD / OLED display panel.

- The video image in frame buffer memory can be 8/10/12-bit 4:2:0 or 4:2:2 or 4:4:4 sampled YCrCb video or 4:4:4 RGB. For 4:2:0 and 4:2:2 YCrCb, the chroma components are re-sampled to 4:4:4 and color converted to RGB.

-

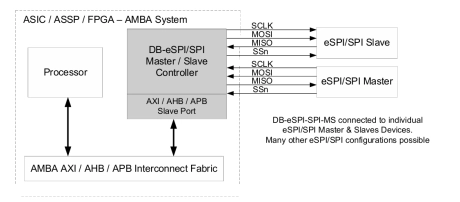

Enhanced SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus. Supports eSPI Master & Slave and SPI Master & Slave functions

- The DB-eSPI-SPI-MS-AMBA is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting the addition of Enhanced SPI (eSPI) bus transfers to the standard SPI Master/Slave Controller. The DB-eSPI-SPI-MS contains an AMBA AXI, AHB, or APB Bus Interface for interfacing a microprocessor to external eSPI or SPI Master/Slave devices.

- The DB-eSPI-SPI-MS contains both eSPI and SPI Master and Slave functions.

-

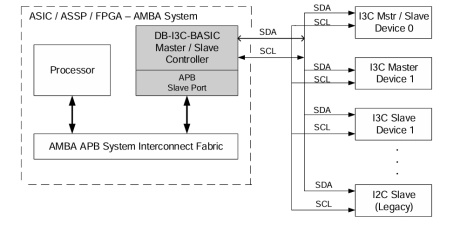

I3C Controller IP – Master / Slave, Parameterized FIFO, APB Bus. I3C Basic Specification Design

- Master / Slave MIPI I3C Controller

- Supports following I3C bus speeds: Single Data Rate (SDR) - up to 12.5 MHz

- I3C Communications Support: I3C SDR / Broadcast / Direct Messages; Legacy I2C Message