PCIe IP

Filter

Compare

899

IP

from

88

vendors

(1

-

10)

-

PCIe PHY and controller solution

- Brite 16Gbps PCIe PHY and controller solution provide high efficient interconnection that is optimized for PPA performance. The System can support short-reach or long-reach channels for plenty application scenarios.

- Brite PCIe controller to AXI architecture provides a high-performance, easy-to-use interconnect solution between PCI Express and the latest version of the AXI protocol. It inherits the leading architecture and features an AXI user interface with built-in DMA, compliant with the AMBA® AXI3 and AXI4 specifications.

-

PCIe Controller

- Dolphin PCIe Controller is a high-performance and compact solution for PCIe provide high-throughput, low-latency, and power-efficient external connectivity in SoCs for mobile, networking, storage, cloud computing, and automotive applications.

- The PCIe Controller consists of silicon-proven digital controllers, PHYs and verification IP, all of which are designed to support all required features of the PCIe 5.0 32GT/s (Gen5), PCIe 4.0 16GT/s (Gen4), 3.1 8GT/s (Gen3), 2.1 5GT/s (Gen2) and 1.1 2.5GT/s (Gen1).

-

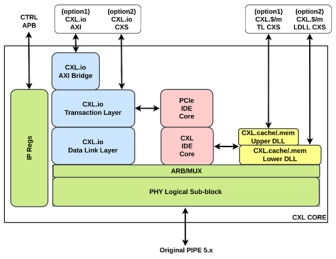

PCIe 4.0 Controller

- PCIe Controller is a high performance PCIE controller, it can support PCIE 1.0/2.0/3.0/4.0 protocol, and the support speed is 2.5G/5G/8G/16G.

- PCIe Controller support dual mode (ROOT mode or Endpoint mode).

- PCIe Controller’s interface with PHY is PIPE 4.0 interface and the PCIe Controller’s interface with application layer is the AXI4.0 interface, and it also has a APB bus for register access.

- The Lane number is configable, it can support X1, X2, X4 lanes.

-

PCIe PHY

- Support for PCIe3(8.0Gbps),Backward compatible with 2.5Gbps and 5Gbps for PCIe

- Full compatible with PIPE4.2 interface specification

- Support 16bit and 32bit parallel data bus

- Independent channel power down control

- Supported reference clock input range from 25M to 400M

-

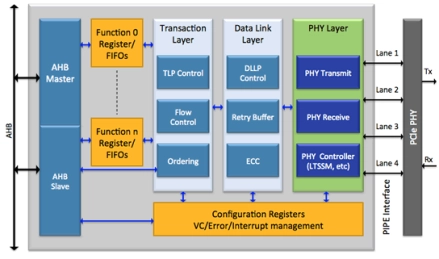

PCIe Controller IP

- The PCI Express® (PCIe®) Controller IP is a highly configurable, performance-optimized core designed for ASIC and FPGA integration.

- Supporting PCIe Gen1 through Gen6 at data rates up to 64 GT/s, the controller accommodates a wide range of link widths (x1–x16) and protocol features to meet the demands of next-generation SoC, networking, and high-performance computing platforms.

- The controller seamlessly interoperates with PIPE-compliant PHYs and supports multiple modes including Root Complex, Endpoint, Switch, and Dual-Mode operation.

-

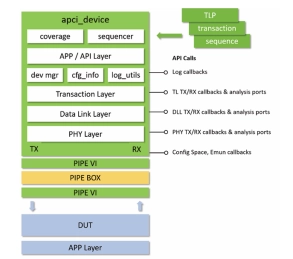

Verification IP for PCIe

- Accelerated confidence in simulation-based verification of RTL designs with PCI Express (PCIe) interfaces: PCIe Gen2/3/4/5/6/7

-

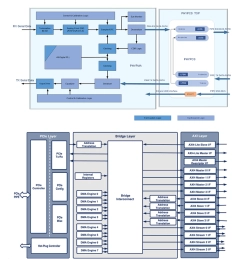

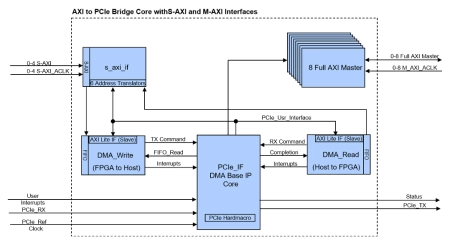

AXI Bridge for PCIe IP Core

- The AXI Bridge for PCIe IP core is the IP solution with a powerful mix of multiple industry standard memory mapped AXI Interfaces.

- The AXI Bridge IP core translates the AXI4 memory read or writes to PCI-Express Transaction Layer Packets and translates PCIe memory read and write requests to AXI4 transactions.

- All interfaces support fully parallel operation without any interferences. Interfaces that are not required can be turned off individually and do not occupy logic resources.

-

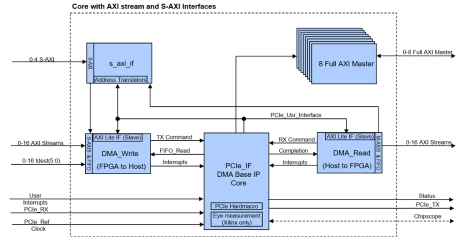

AXI Bridge with DMA for PCIe IP Core

- The AXI Bridge with DMA IP core is the ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces.

- AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or per to peer applications.

-

PCIe End Point IP Core

- The PCI Express End Point is a high-speed, high-performance, and low-power IP core that is fully compliant to the PCI Express Specification 1.1 and 2.0.

- The IP core is designed for applications in computing, networking, storage, servers, wireless, and consumer electronics.