PCI Express 3.0 IP

Filter

Compare

121

IP

from

18

vendors

(1

-

10)

-

PCIe - PCI Express Controller

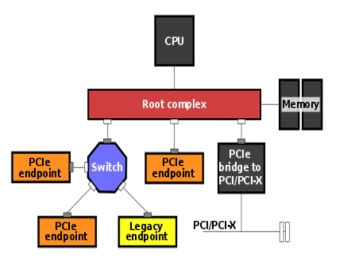

- The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect various components to a computer's motherboard.

- It is the third generation of the PCIe standard and offers increased bandwidth, improved performance, and reduced power consumption compared to its predecessor, PCIe 2.0 Overall, PCIe 3.0 provides faster and more efficient communication between the various components in a computer, including graphics cards, network adapters, and storage devices, resulting in better overall performance.

-

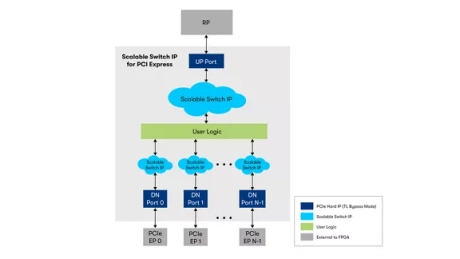

Scalable Switch Intel® FPGA IP for PCI Express

- The Scalable Switch Intel® FPGA IP for PCI Express is a fully configurable switch that implements one fully configurable upstream port and connectivity for up to 64 downstream ports.

-

PCI Express Gen3/Enterprise Class SERDES PHY on Samsung 28LPP

- Industry leading low power PMA macro – 88mW per lane at 8Gbps (11.0 mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.216 mm2 active silicon area per lane including ESD

- Enterprise class Long Reach 5-tap DFE supporting beyond standard PCIe Channels

- Minimal latency – 3 UI between parallel transfer and serial transmission

-

PCI Express Gen3 SERDES PHY on Samsung 7LPP

- Industry leading low power PMA macro – 36mW per lane at 8Gbps (4.5mW/Gbps) inclusive of Tx and Rx PLLs, termination, bias, etc.

- Compact form factor – 0.1 mm2 active silicon area per lane including ESD

- Minimal latency – 3 UI between parallel transfer and serial transmission

- Single-lane macro scalable to unlimited link width – x1, x2, x4, x8, x16, etc.

-

PCI Express Gen3 / SATA3 SERDES PHY on Samsung 28FDSOI

- Programmable SERDES analog front end that supports 1 to 8 Gbps standard serial protocols

- Compact form factor – 0.165 mm2 active silicon area per lane including ESD

- Industry leading low power – typically 6.5 mW/Gbps including termination

- Finely configurable receiver impedance, CTLE gain and bandwidth, with fully adaptive CTLE and DFE

-

PCI Express PHY

- Quad PCIe 16/8/5/2.5 Gbps per lane

- Tight control over termination resistor (~50 Ohm) with on chip calibration

- Tight skew control of 1UI between lanes of the PMA

- 3-tap Tx Finite Impulse Response (FIR) equalizer with multi-level de-emphasis

-

Virtex-7 FPGA Gen3 Integrated Block for PCI Express (PCIe)

- Compliant with the PCI Express Base Specification 3.0

- Supported Lane width: x1, x2, x4 and x8

- Fully compliant with PCI Express transaction ordering rules

- Optimal buffering for high bandwidth Direct Memory Access (DMA) applications

-

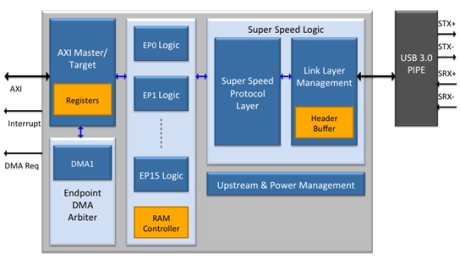

USB 3.0 Device Upgrade IP Core

- The USB 3.0 Device Upgrade provides a dedicated dual simplex, routable packet architecture for USB3.0 packet transfers, with a disable option for power savings.

- The USB 3.0 Upgrade IP supports all power management features as well as a dedicated link manager for each downstream port for increased efficiency.

-

USB 3.0 Device

- USB 3.0 Compliance

- SuperSpeed: 5 Gbit/s

- Hish Speed: 480Mbit/s

- Full Speed: 12Mbit/s

- 8/16/32 bit USB 3.0 PIPE interface

-

PCIe 3.0 PHY, UMC 28HPC x4, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 3.1, 2.1, 1.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE)

- L1 substate and SRIS support