Octal SPI Flash Interface IP

Filter

Compare

21

IP

from

10

vendors

(1

-

10)

-

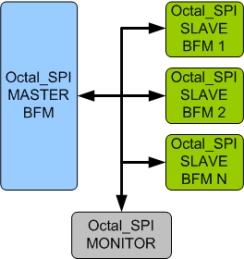

Octal SPI (Serial Peripheral Interface) Verification IP

- Follows Octal SPI basic specification as defined in Macronix (CMOS MXSMIO®(SERIAL MULTI I/O) Flash memory).

- Supports Master and Slave Mode.

- Supports Serial Peripheral Interface -- Mode 0

- Supports below Protocol modes

-

Host controller IP for controlling flash and other devices on the SPI bus: Quad SPI, Octal SPI, and xSPI

- Flexibility: Multiple SPI protocol support within single IP

- Simplicity: PHY-less IoT operation, or soft storage combo PHY IP simplifies SoC timing

- High Performance: Supports maximum Quad SPI / Octal SPI data rates and XIP (Execute In Place)

-

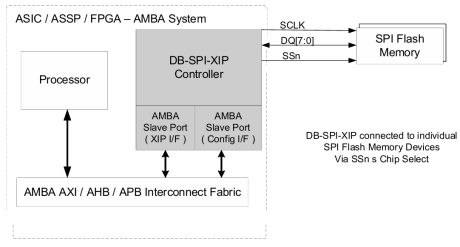

SPI XIP Flash Memory Controller IP – Programmable IO & Execute-In-Place (XIP) via second AMBA Interface

- The DB-SPI-XIP-FLASH-AMBA is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting access to Single/Dual/Quad/Octal SPI Flash Memory devices by way of Processor Execute-in-Place (XIP).

- The DB-SPI-XIP-FLASH-AMBA is a SPI Master Controller targeting SPI NOR/NAND Flash Memories. The DB-SPI-XIP-FLASH-AMBA contains two AMBA Slave Interfaces: the first for Processor configuration or Processor access to the Flash Memory; the second for Processor AMBA Interface for Execute-in-Place (XIP) access to Flash Memory.

-

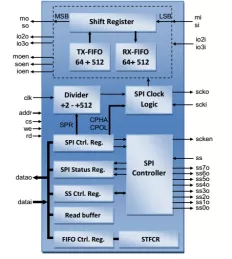

FSPI Controller – XIP functionality (SINGLE, DUAL, QUAD and OCTAL SPI Bus Controller with Double Data Rate support)

- Set of software accessible control registers to

- execute any Flash memory command

- Support for most popular SPI like FLASH memories and PSRAM

- Supports any device clock frequency, polarity and phase

-

SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption)

- Set of software accessible control registers to execute any Flash memory command

- Supports any device clock frequency, polarity and phase,

- Programmable baud rate generator,

- Built in FLASH Commands decoder supports most popular FLASH devices,

-

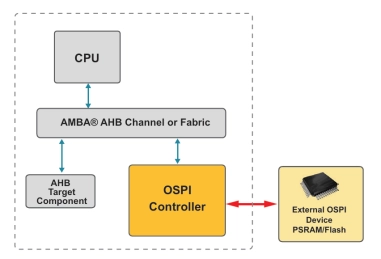

AHB Octal SPI Controller with PSRAM and XIP Support

- The Octal SPI Memory Controller IP core is a serial peripheral interface (SPI) master which controls an external serial device, usually an industry-standard FLASH or PSRAM memory device.

- In Software Mode, an AHB Master may access the register interface of the Controller to implement a wide range of protocol variants and/or commands on the SPI bus.

-

QSPI FLASH Controller – XIP functionality (SINGLE, DUAL and QUAD SPI Bus Controller with Double Data Rate support)

- Set of software accessible control registers to execute any Flash memory command

- Supports any device clock frequency, polarity and phase,

- Programmable baud rate generator,

- Built in FLASH Commands decoder supports most popular FLASH devices,

-

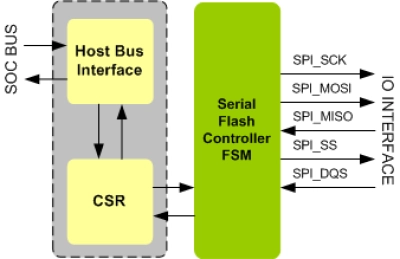

Serial Flash Controller IIP

- Compliant with Flash Devices from major Flash Device Vendors.

- Full Flash with SPI Master Functionality.

- Supports 3 modes of operation

- Slave Mode - Accessing flash device through CSR registers from SOC Slave interface

-

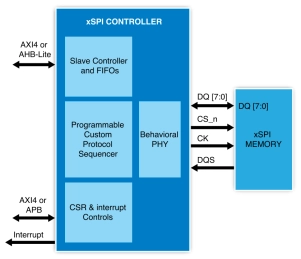

xSPI NOR/NAND Flash & HyperRAM Controller

- Memory mapped access to the connected flash devices

- Continuous Burst transfer support

- Auto boot support

-

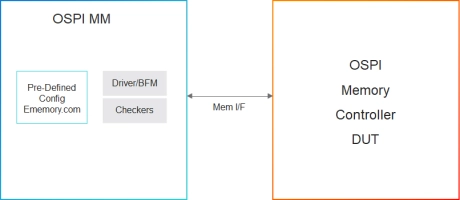

Simulation VIP for OSPI NOR

- Device Density

- From 256Mb to 2Gb, with frequency up to 133MHz in SPI and 200MHz in OSPI mode

- Operation Mode

- Extended SPI mode, Octal SDR and DDR mode (Single I/O and Octal I/O)