MIPI DSI-2 TX Controller IP

Filter

Compare

6

IP

from

5

vendors

(1

-

6)

-

MIPI DSI-2 Transmitter v1.1 Controller IP, Compatible with MIPI D-PHY & C-PHY

- Compliant with MIPI DSI-2 Standard v0.8.x, MIPI D-PHY Standard v1.x, MIPI D-PHY Standard V2.x and MIPI C-PHY V1.x

- Up to 3 Gsps per trio using C-PHY. 17Gbps in 3 Trios

- Up to 2.5 Gbps per data lane of D-PHY (V2.0). 10Gbps in 4 Lanes

- Programmable 1, 2, 3 (C-PHY) or 4 (D-PHY) Data Lane Configuration

-

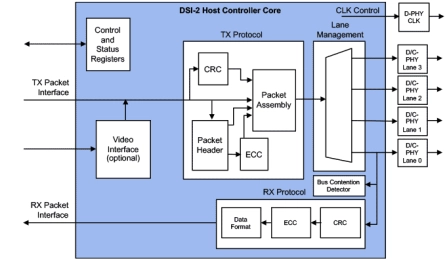

MIPI DSI-2 Controller Core

- Fully MIPI DSI-2/DSI standard compliant

- 64 and 32-bit core widths

- Host (Tx) and Peripheral (Rx) versions

- Supports 1-4, 9.0+ Gbps D-PHY data lanes

- Supports 1-4, 6.0+ Gsym/s C-PHY lane (trio)

- Supports all data types

-

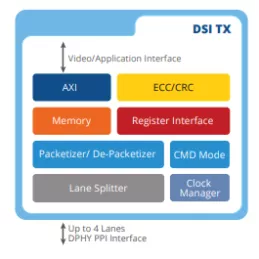

MIPI DSI-2 Transmitter Controller IP Core

- The MIPI Display Serial Interface (DSI-2) Transmitter (host processor interface) Controller IP provides a high-speed serial interface between an application processor and display modules using either MIPI C-PHY v1.1 or MIPI D-PHY v1.2 and v2.0.

-

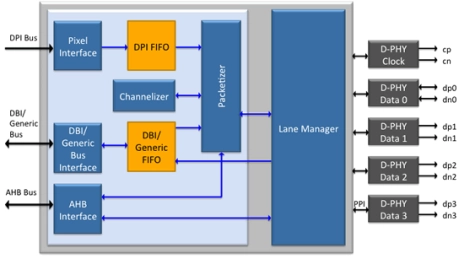

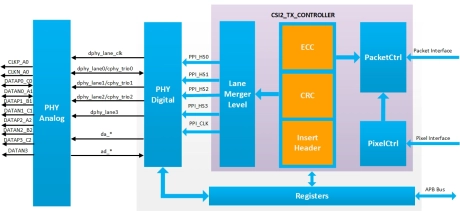

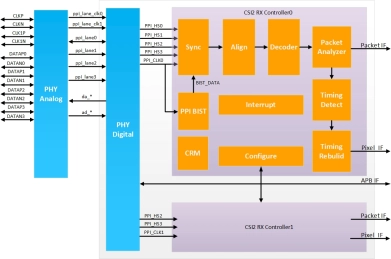

MIPI C/D-PHY CSI/DSI TX and RX

- The MIPI C/D-PHY + DSI/CSI Controller IP is a versatile solution designed for high-speed data transmission in mobile and multimedia applications

- It integrates C-PHY and D-PHY in a single IP core, supporting both MIPI C-PHY 1.1 and D-PHY 2.0 standards

- The IP features a compact design with built-in I/O and ESD protection, optimized for robust performance and low power consumption

-

MIPI D-PHY1.2 CSI/DSI TX and RX

- The MIPI D-PHY + DSI/CSI Controller IP is a versatile solution designed for high-speed data transmission in mobile and multimedia applications

- It supports MIPI D-PHY 2.0 standards

- The IP features a compact design with built-in I/O and ESD protection, optimized for robust performance and low power consumption

- It enables seamless connectivity with D-PHY based sensors, making it ideal for SoCs in consumer electronics, automotive, and IoT devices

-

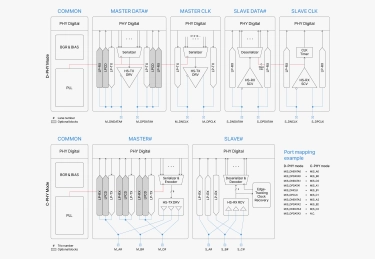

MIPI C/D-PHY Combo IP

- Compliant to MIPI D-PHY v3.0, C-PHY v2.1 specification

- Area efficient macro optimized for placement for dense SoC designs

- Support Uni-(TX or RX) and Bi-directional(TX and RX) mode

- Support emphasis architecture over lossy channel for TX

- Support equalize architecture over lossy channel for RX