MCMR FEC IP

Filter

Compare

3

IP

from

3

vendors

(1

-

3)

-

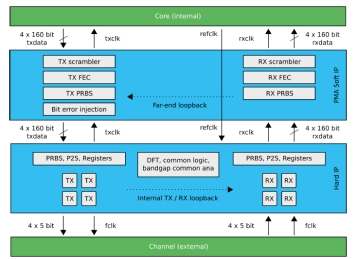

UCIe Chiplet PHY & Controller

- Compliant with the UCIe specification (2.0 & 1.1)

- Flexible Structure, easy to customize (Pre-hardened PHY tuned to Customer Spec, PHY + Adapter Layer, PHY + Adapter Layer + Customized Protocol Layer)

- Supports the CXS/AXI using the streaming package (AXI Interface bandwidth up to 89%)

-

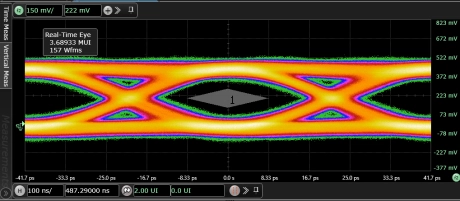

Ultra-short reach SerDes with 500 Gbit/s throughput

- 2x to 4x throughput at 50% or less energy consumption as compared to conventional SerDes over the same number of pins/wires

- High pin-efficiency and low power

- 208.3 Gbit/s full-duplex bandwidth per mm of die edge (500 Gbit/s for 2.4 mm of die edge)

-

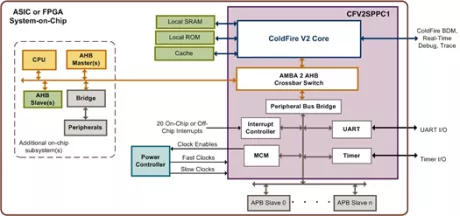

ColdFire V2 Core with AMBA peripherals connected in a subsytem

- Building upon the 68K foundation, ColdFire offers RISC performance with industry-leading code density and a rich set of connectivity peripherals.

- By supporting variable-length instructions (16-, 32- or 48-bits long), the ColdFire Architecture enables higher code density than traditional 32- and 64-bit RISC machines.

- More efficient use of on-chip memory reduces bus bandwidth and external memory requirements, resulting in lower system cost.