LPDDR3/4 Single Controller IP

Filter

Compare

127

IP

from

7

vendors

(1

-

10)

-

Universal Multi-port Memory Controller for RLDRAM2/3, DDR4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

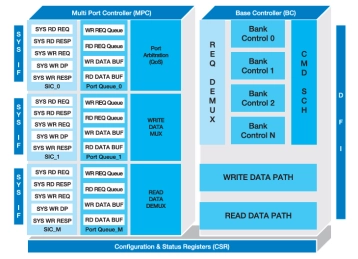

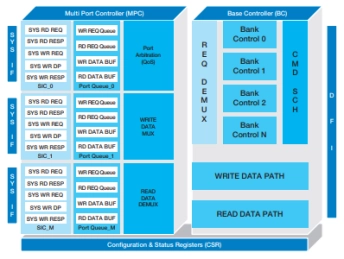

- The UMMC Controller is a highly flexible and configurable design. It is targeted for high bandwidth access and low power consumption such as next generation mobile, DDR/LPDDR networking and consumer applications.

- The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities.

-

Universal Multi-port Memory Controller for RLDRAM2/3, DDR5/4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- The UMMC (Universal Multi-port Memory Controller for RLDRAM2/3, DDR5/4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2) is a highly flexible and configurable design that supports RLDRAM2, RLDRAM3 and JEDEC compliant DDR5, DDR4 3DS, DDR4, DDR3, LPDDR3, LPDDR3 and LPDDR2 memories.

- It is targeted for high bandwidth access and low power consumption such as next-generation mobile, networking and consumer applications. The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities

-

SDRAM DDR Controller

- Dolphin Technology offers high performance DDR4/3/2 SDRAM and LPDDR5/4x/4/3/2 SDRAM Memory Controller IP across a broad range of process technologies.

-

LPDDR Controller

- Memory controller interface complies with DFI standard up to 5.0

- Application-optimized configurations for fast time to delivery and lower risk

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 protocol memories

- Priority per command on Arm®AMBA® 4 AXI, AMBA 3 AXI

-

LPDDR4X/4 & LPDDR5T/5X/5 Combo Controller

- Support for all LPDDR4 and LPDDR5 devices

- Bank management logic monitors status of each bank

-

LPDDR4 multiPHY V2 in UMC (28nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4 multiPHY V2 in Samsung (8nm) for Automotive

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4 multiPHY V2 in GF (22nm) for Automotive

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4 multiPHY V2 in GF (22nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

TSMC CLN40LPP 40nm LPDDR4 PHY - 2933Mbps

- Supports LPDDR4

- DFI 5.1 compliant

- Supports x4, x8 and x16 DRAMs

- Up to 72 bits wide and up to 4 ranks