ISO 26262 RISC-V Processor IP

Filter

Compare

11

IP

from

5

vendors

(1

-

10)

-

32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification

- Flexible use cases

- roven technology

- State-of-the-art safety and security

-

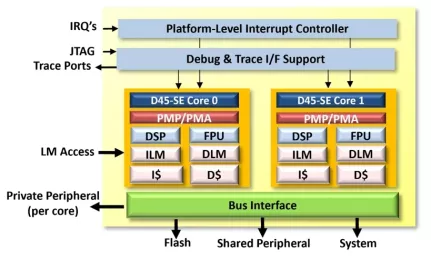

8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

- The 32-bit D45-SE is an 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications.

-

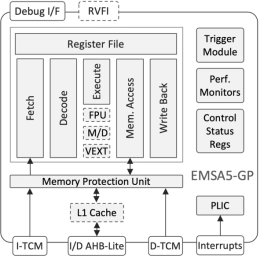

Vector-Capable Embedded RISC-V Processor

- The EMSA5-GP is a highly-featured 32-bit RISC-V embedded processor IP core optimized for processing-demanding applications.

- It is equipped with floating-point and vector-processing units, cache memories, and is suitable for concurrent execution in a multi-processor environment.

-

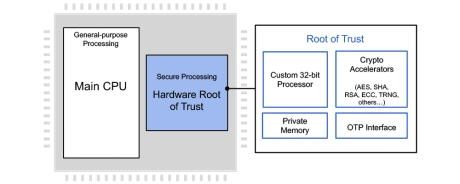

Embedded Hardware Security Module (Root of Trust) - Automotive Grade ISO 26262 ASIL-B

- The RT-64x Embedded Hardware Security Module (Root of Trust) family are fully programmable, ISO 26262 ASIL-B hardware security cores offering security by design for automotive applications.

- They protect against a wide range of failures such as permanent, transient and latent faults and hardware and software attacks with state-of-the-art anti-tamper and security techniques.

-

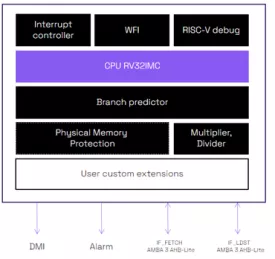

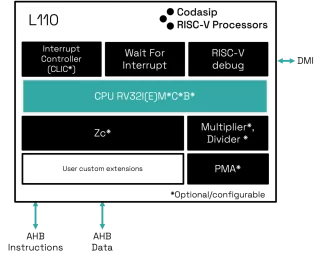

32 Bit - Embedded RISC-V Processor Core

- Best-in-class performance for small-area and low-power applications

- Highly configurable and easy and quick to customize and verify

- Process compliant with ISO 26262 and ISO 21434

-

Embedded HSM Family (Root of Trust) - Automotive Grade ISO 26262 ASIL-B

- Custom-designed 32-bit RISC-V secure processor

- Security model include hierarchical privilege model, secure key management policy, hardware-enforced isolation/access control/protection, error management policy

- Standard hardware cryptographic accelerators, including AES (all modes), HMAC, SHA-2 (all modes), RSA up to 4096 bits, ECC up to 521 bits, a NIST-compliant Random Bit Generator, AXI Multi Issue Out-of-Order, and Fast DMA capability. Additional algorithms such as Whirlpool (SHE), SHA-1 (legacy), AES-CMAC, SHA-3, Poly1305, ChaCha and OSCCA SM2-3-4 are available

- Multi-layered security model protects all core components against a wide range of attacks

-

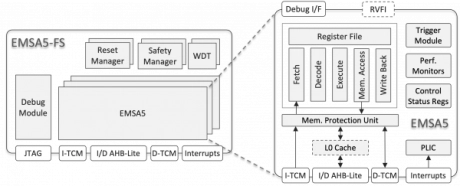

32-bit Embedded RISC-V Functional Safety Processor

- The EMSA5-FS is a processor core designed for functional safety.

- The fault-tolerant processor uses dual or triple instances of the EMSA5, an efficient 32-bit embedded processor IP core implementing the RISC-V Instruction Set Architecture (ISA).

-

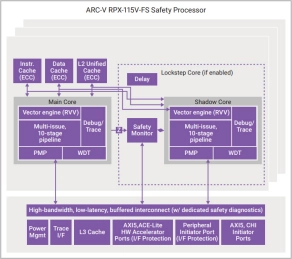

ARC-V RPX Series Functional Safety Processor IP

- The ARC-V™ RPX-110 series functional safety (FS) processors, which include the RPX-110-FS, RPX-115-FS, RPX-110V-FS, and RPX-115V-FS processors simplify development of high-performance safety-critical applications and accelerate ISO 26262 certification for automotive system-on-chips (SoCs).

- The Automotive Safety Integrity Level (ASIL) D compliant processors feature a pre-verified dual-core lockstep implementation including an integrated safety monitor.

- Additionally, they offer the flexibility to operate in an independent “hybrid” mode for ASIL B or non-automotive applications that demand higher performance from the same design.

-

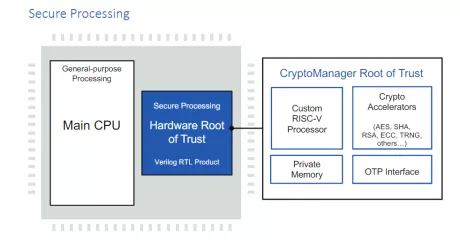

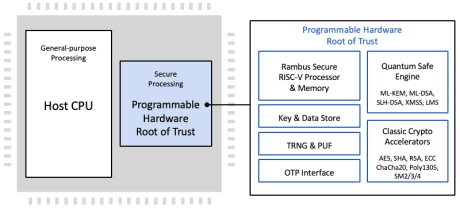

Quantum Safe, ISO 21434 Automotive-grade Programmable Hardware Security Module

- The automotive-grade CryptoManager RT-7xx v3 Root of Trust family is the next generation of fully programmable ISO 26262 and ISO 21434 compliant hardware security modules offering Quantum Safe security by design for secure automotive applications.

- The CryptoManager RT-7xx family protects against a wide range of hardware and software attacks through state-of-the-art side channel attack countermeasures and anti-tamper and security techniques.

-

ISO26262 ASIL-B/D Compliant 32-bit RISC-V Core

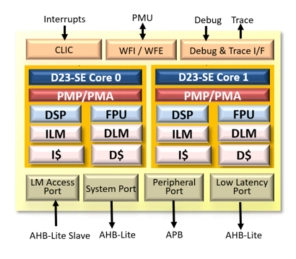

- The AndesCore™ D23-SE is a 32-bit 3-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications with small gate count, and some dual-issue ability.

- In addition to commonly used RISC-V IMAC, single/double precision FPU and DSP extensions, it supports the recently ratified ISA extensions such as B (bit manipulation), K (scalar cryptography), CMO (cache management operations) as well as Zce (code size reduction), plus Andes Custom Extension™ (ACE) for user-defined instructions.