IEEE 802.3bz IP

Filter

Compare

186

IP

from

25

vendors

(1

-

10)

-

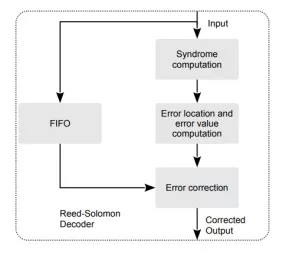

25G IEEE 802.3by Reed-Solomon Forward Error Correction

- Run-time switchable between IEEE802.3by and 25G Ethernet Consortium Schedule 3 specification mode

- Low latency

- Accessible as integrated feature in the 25G Ethernet Subsystem

- Configuration and status bus

-

IEEE 802.3bj Reed-Solomon Forward Error Correction

- Low latency

- Supports 100 Gigabits

- Configuration and status bus

- Selectable AXI4-Lite interface for status output

-

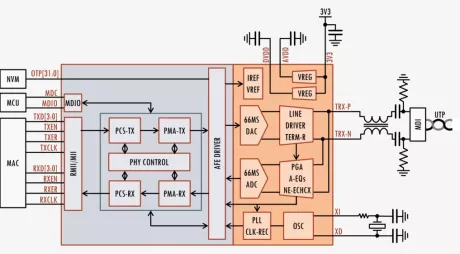

100BASE-T1 (OABR) Ethernet PHY IEEE 802.3bw Compliant

- OABR V3.2 Compliant

- IEEE 802.3bw Compliant

- IEEE 1588 PTP Support under design

-

IEEE 802.3bj Reed-Solomon Encoder and Decoder

- Compliant with IEEE 802.3bj, Clause 91

- Support for KR4 (528, 514) and KP4 (544, 514) Reed-Solomon (RS) code

- Corrects up to seven (KR4) or up to 15 (KP4) erroneous symbols

-

100G Reed-Solomon Codec for Ethernet IEEE 802.3 Clause 91 (803.3bj)

- FEC Sublayer for 100GBASE-CR4 and 100GBASE-KR4 PHY (clause 91 of the IEEE 802.3bj standard).

- 100G Ethernet MAC-friendly interface

-

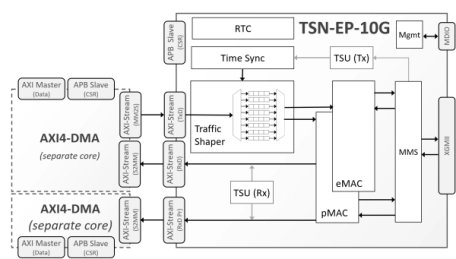

TSN Ethernet Endpoint Controller 10Gbps

- The TSN-EP-10G implements a configurable controller meant to ease the implementation of endpoints for networks complying with the Time Sensitive Networking (TSN) standards

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020) and traffic shaping (IEEE 802.1Qav and 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.

-

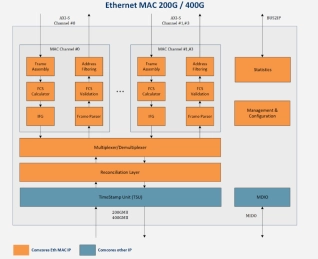

Ethernet MAC 200G/400G

- The 200G/400G Ethernet Media Access Control (MAC) IP core provides a comprehensive and flexible solution for implementing the IEEE 802.3 MAC layer for high-speed Ethernet required in demanding applications such as hyperscale data centers, high-performance computing (HPC), and Artificial Intelligence (AI) / Machine Learning (ML) clusters.

-

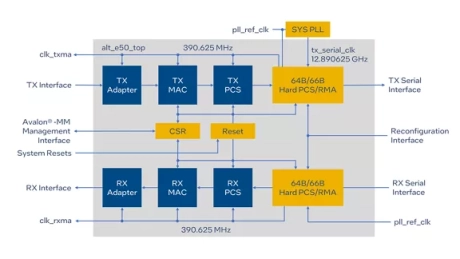

50G Ethernet Intel® FPGA IP

- The 50G Ethernet Intel® FPGA IP core implements the 25G & 50G Ethernet Specification, Draft 1.4 from the 25 Gigabit Ethernet Consortium and the IEEE 802.3by 25Gb Ethernet draft

- The IP core includes an option to support unidirectional transport as defined in Clause 66 of the IEEE 802.3-2012 Ethernet Standard

- The MAC client side interface for the 50 Gbps Ethernet IP core is a 128-bit Avalon® streaming interface (Avalon-ST)

-

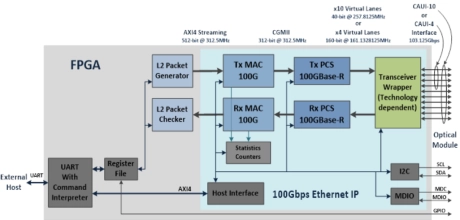

100 G Ethernet MAC & PCS IP Core

- The 100 Gbps Ethernet IP solution offers a fully integrated IEEE802.3ba compliant package for NIC (Network Interface Card) and Ethernet switching applications.

- Ethernet IP solution implements two user (application) side interfaces. The register configuration and control port is a 32-bit AXI4-Lite interface.

-

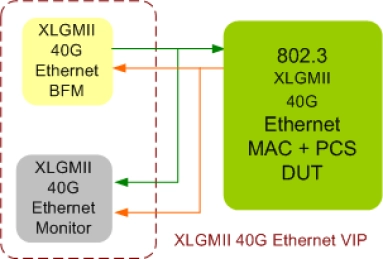

XLGMII 40G Ethernet Verification IP

- Follows XLGMII specification as defined in IEEE 802.3ba

- Supports all types of XLGMII TX and RX errors insertion/detection

- Oversize, undersize, inrange, out of range Packet size errors

- Missing SPD/EPD/SFD framing errors