I2C Controller IP

-

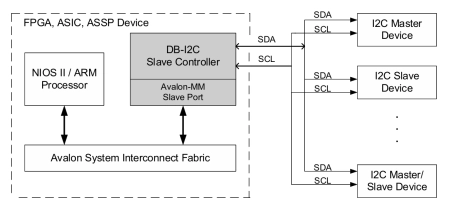

I2C Controller IP – Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-S-AHB Controller IP Core interfaces a NIOS II, ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the Avalon System Interconnect Fabric to an I2C Bus.

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

-

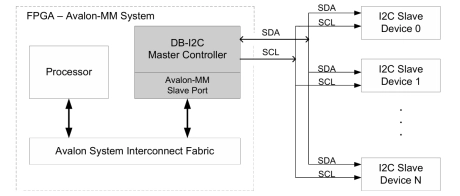

I2C Controller IP – Master, Parameterized FIFO, Avalon Bus

- The DB-I2C-M-AVLN Controller IP Core interfaces a microprocessor via the Avalon Bus to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-M-AVLN is a Master I2C Controller that controls the Transmit or Receive of data to or from slave I2C devices. In an Altera FPGA, typically, the microprocessor is a NIOS II processor, but can be any FPGA embedded processor. Figure 1 depicts the system view of the DB-I2C-M-AVLN Controller IP Core embedded within an FPGA integrated circuit device.

-

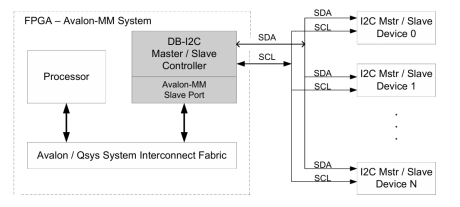

I2C Controller IP- Master / Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-MS-AVLN Controller IP Core interfaces a microprocessor via the Avalon Bus to an I2C Bus in Standard-Mode (100 Kbit/s) / Fast-Mode (400 Kbit/s) / Fast-Mode Plus (1 Mbit/s) / Hs-Mode (3.4+ Mb/s) / Ultra Fast-Mode (5 mbit/s).

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-MS-AVLN is a Master / Slave I2C Controller that in Master Mode controls the Transmit or Receive of data to or from slave I2C devices while in Slave Mode allows an external I2C Master device to control the Transmit or Receive of data.

-

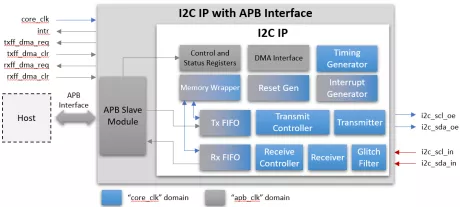

I2C Controller

- Dual mode IP (master and slave mode).

- Supports different modes of transfer .

- Supports DMA interface also .

- Separate clock domain for IP Core functionality and Host Interface.

-

I2C Controller IP – Slave, Parameterized FIFO, AHB Master Interface (I2C2AHB)

- The DB-I2C-S-AHB-BRIDGE is an I2C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs not requiring internal configuration & control registers (and thus no local host CPU required), and an AHB Master interface for read/write to the user system.

- The DB-I2C-S-AHB-BRIDGE processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload via a bridge AHB Master Interface to user registers or memory.

-

I2C Controller IP – Slave, Parameterized FIFO, AXI Master Interface (I2C2AXI)

- The DB-I2C-S-AXI-BRIDGE is an I2C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs not requiring internal configuration & control registers (and thus no local host CPU required), and an AXI Master interface for read/write to user system.

- The DB-I2C-S-AXI-BRIDGE processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload via the bridge AXI Master Interface to user registers or memory.

-

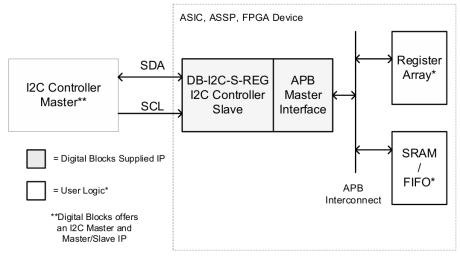

I2C Controller IP – Slave, Parameterized FIFO, APB Master Interface (I2C2APB)

- The DB-I2C-S-APB-BRIDGE is an I2C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs not requiring internal configuration & control registers (and thus no local host CPU required).

- The DB-I2C-S-APB-BRIDGE processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload via a bridge APB Master Interface to user registers or memory.

-

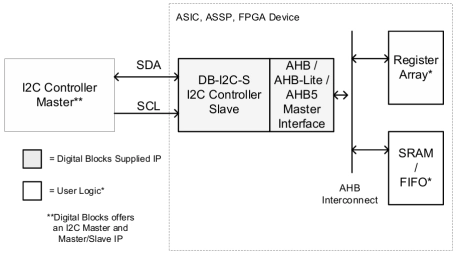

I2C Controller IP – Slave, Parameterized FIFO, AHB Bus

-

The DB-I2C-S-AHB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the AMBA 2.0/3.0 AHB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

The DB-I2C-S-AHB is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB I2C-S-AHB Controller IP Core embedded within an integrated circuit device.

-

-

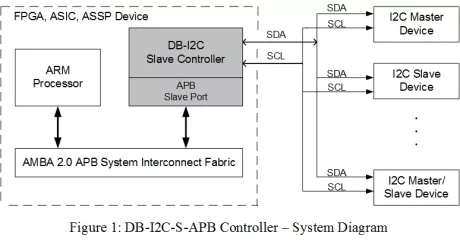

I2C Controller IP – Slave, Parameterized FIFO, APB Bus

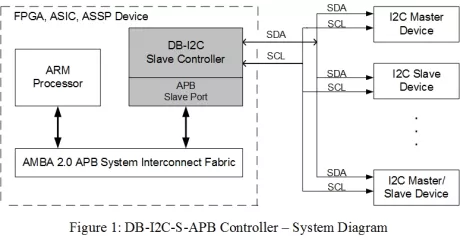

- The DB-I2C-S-APB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high performance microprocessor via the AMBA 2.0 APB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

- The DB-I2C-S-APB is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB I2C-S-APB Controller IP Core embedded within an integrated circuit device.

-

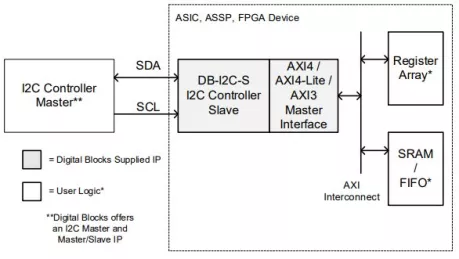

I2C Controller IP – Slave, Parameterized FIFO, AXI Bus

-

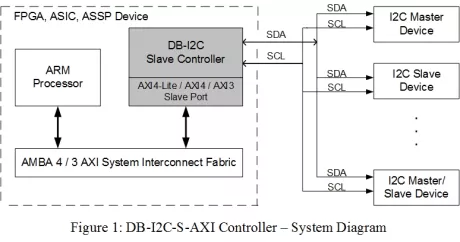

The DB-I2C-S-AXI Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the AMBA 4/3 AXI System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

The DB-I2C-S-AXI is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB I2C-S-AXI Controller IP Core embedded within an integrated circuit device.

-