HMC IP

Filter

Compare

8

IP

from

6

vendors

(1

-

8)

-

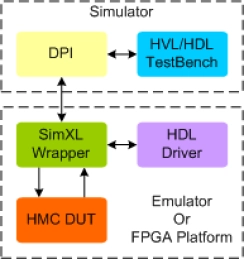

HMC Synthesizable Transactor

- Supports 100% of HMC protocol standard 1.0, 2.0 and 2.1

- Supports all the HMC commands as per the specs

- Supports 2,4 and 8 link configuration

- Supports for half width(8-lanes) and full width(16-lanes)

-

HMC Memory Model

- Supports 100% of HMC protocol standard 1.0,2.0 and 2.1

- Supports all the HMC commands as per the specs.

- Quickly validates the implementation of the HMC standard.

- Supports 2,4 and 8 link configuration

-

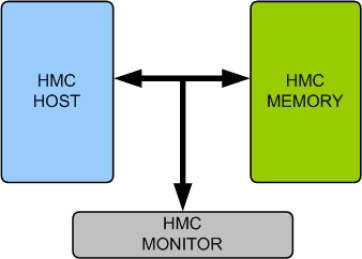

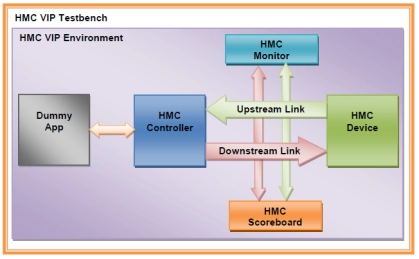

HMC2 Verification IP

- Compliant with Standard HMC Version 2.0 specification.

- Supports 4GB configuration - 256 memory banks and 8GB configuration – 512 memory banks.

- Supports Closed-bank memory architecture.

- Supports Built-in memory controller for each vault – Automatic refresh control over all temperatures.

-

Xilinx HMC Controller

- Fully compliant with Hybrid Memory Cube Specification Revision 1.x

- Support 10 Gb/s, 12.5 Gb/s, 15 Gb/s SerDes I/O interface

- Support either GTH or GTY transceiver use

- Support both HMC link modes

-

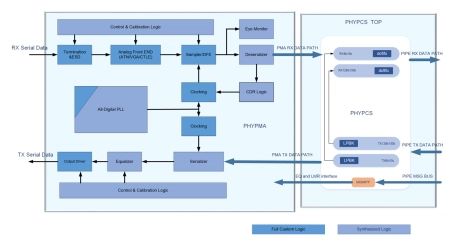

SerDes

- High-speed SerDes with ultra-low-power consumption

- Industry’s fastest die to die communications

- Multiprotocol SerDes: HMC, PCIe, SATA, SAS, and USB and more

- High lane count with multiple data rates supported

-

Multi-Rate Serdes IP Solution

- YouPHY-Serdes provides 2.5-32Gbps multi-rate SERDES IP which is designed for smooth integration of Multiple SERDES lanes demonstrate good performance class performance, area and power.

- The programmable PHY supports major standards such as PCIe Gen 4.0/3.0/2.0/1.0, USB 3.1/3.0, XAUI, SATA Gen 3.0/2.0/1.0, CEI-11G-LR, 10GBase-KX4, JESD204B, SGMII/QSGMII, RAPID I/O, HSSTP (Trace Port), V-By-One, DisplayPort and HMC.

-

UltraScale FPGAs Transceivers Wizard

- Creates customized protocol presets to configure high-speed serial transceivers in UltraScale FPGAs

- Protocol presets provided for 10GBASE-R, 10GBASE-KR, 3G-SDI, Aurora 8B/10B, Aurora 64B/66B, CAUI-4, CAUI-10, CEI-11G, CPRI™, Gigabit Ethernet, HD-SDI, HMC, Interlaken, JESD204B, MoSys Bandwidth Engine, OTL 4.10, OTU2/2e, OTU4, QSGMII, RXAUI, SATA, Serial RapidIO Gen2, XAUI, XLAUI, and DisplayPort.

-

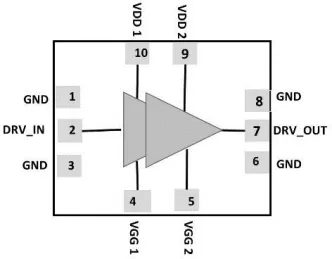

Driver Amplifier operating from 24-30 GHz and can be used in wide band application or to drive the high-power amplifier

- RF Frequency: 24-30 GHz

- Gain of 13.6 dB

- Output P1dB of 24.9 dBm

- Noise Figure of 3 dB