DMA IP

Filter

Compare

586

IP

from

102

vendors

(1

-

10)

-

DMA Controller

- DTI_DMA control the DMA transfers data between different points in the memory space without intervention of the CPU.

- The DMA is generally used to replace two CPU functions: memory copy and transfer data between memory and peripheral (peripheral devices such as SPI, UART, GPIO, I2C, I2S, WDT, etc.)

-

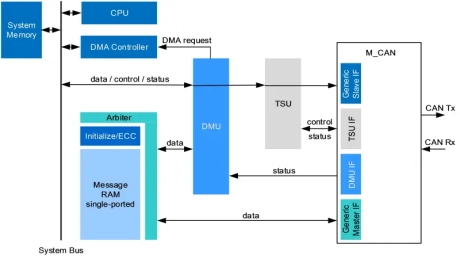

DMA Unit

- The DMU signals to the attached DMA Controller (DMA request) when there is a newly received message available at one of the attached M_CAN's Rx FIFOs respectively when there is the possibility to load a new Tx message into the M_CAN's Tx FIFO/Queue.

- The DMA controller then autonomously transfers the received message from the M_CAN's Message RAM to the System Memory or the message to be transmitted from the System Memory to the M_CAN's Message RAM.

-

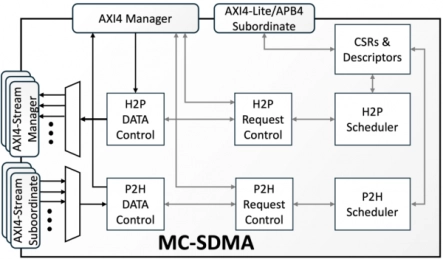

Multi-Channel Streaming DMA Controller

- The MC-SDMA IP core implements a highly configurable, bandwidth-efficient, and easy-to-use Direct Memory Access (DMA) controller that transfers data between the host system’s memory and multiple peripherals equipped with streaming interfaces.

- The core interfaces with the host memory via a manager AMBA® AXI4 (memory-mapped) port and provides access to its configuration and status registers (CSRs) via a subordinate AXI4-Lite or APB4 interface.

-

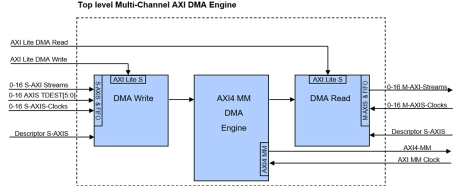

Multi-Channel AXI DMA Engine

- The Multi-Channel AXI DMA engine IP Core for AXI4 is a powerful programmable AXI Stream to AXI memory mapped bridge with sophisticated data addressing options.

- These features allow data accesses on a tile basis in order to address regions of interest (ROI) based applications like stereo cameras, 2D picture compression algorithms and others.

-

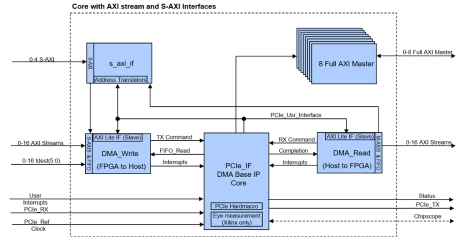

AXI Bridge with DMA for PCIe IP Core

- The AXI Bridge with DMA IP core is the ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces.

- AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or per to peer applications.

-

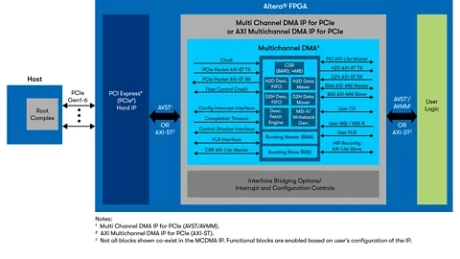

Multichannel DMA Intel FPGA IP for PCI Express*

- The Multichannel DMA IP for PCI Express provides high efficiency, speed, and configuration flexibility to support various applications from HPC, cloud, networking, to embedded

- With support for up to 2048 channels and Linux-based PCIe drivers provided, this low latency, low resource utilization solution is essential in handling movements of large volumes of data to optimize system performance.

-

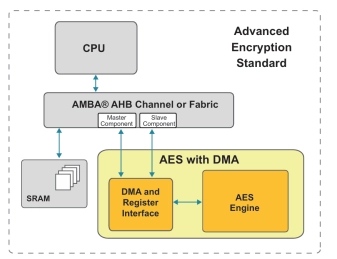

AHB AES with DMA

- The Advanced Encryption Standard (AES) IP Core is a complete hardware implementation encryption/decryption algorithm described in the U.S. Government Federal Information Processing Standards Publication 197 (FIPS 197).

- The AES IP Core implements the Rijndael algorithm which is a symmetric block cipher that can process 128-bit data blocks using 128, 192, or 256-bit cipher keys.

-

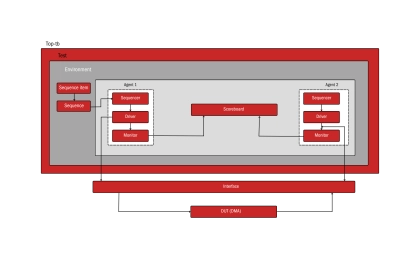

Scatter Gather DMA Engine - Validates efficient scatter-gather DMA for high-performance data transfer

- The Scatter-Gather DMA Engine Verification IP (VIP) is designed to validate the functionality and performance of scatter-gather DMA controllers in SoCs. It ensures efficient data transfer between non-contiguous memory regions while minimizing CPU utilization, offering features like protocol compliance and transaction monitoring.

- Ideal for applications such as networking, multimedia, storage, and embedded systems, the VIP helps ensure high-performance, reliable data movement. It supports multi-channel configurations, error injection, and performance monitoring to optimize system efficiency and robustness

-

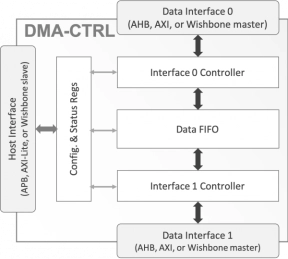

AHB/AXI/Wishbone DMA Controller

- The AXI4-SGDMA IP core implements a Host-to-Peripheral (H2P), or a Peripheral-to-Host (P2H) Direct Memory Access (DMA) engine, which interfaces the host system with an AXI4 Memory-Mapped master port and the peripheral with either a slave or a master AXI4-Stream port.

- The core operates in either Scatter-Gather (SG) Mode, reading descriptors from a run-time defined memory mapped-location, or in Direct Mode, transferring data according to a descriptor stored in local registers.

-

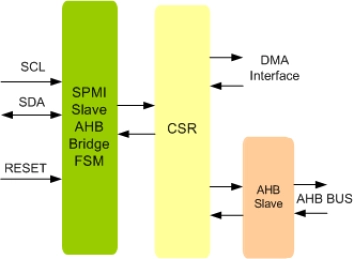

MIPI SPMI Slave DMA IIP

- Supports 2.0 and 1.0 MIPI SPMI Specification

- Full MIPI SPMI Slave functionality

- Supports following frames

- Command Frame