DDR3 IP

Filter

Compare

239

IP

from

40

vendors

(1

-

10)

-

DDR3 and DDR4 Controller and PHY on TSMC 12nm

- This DDR3/4 IP combo solution presented, is meticulously designed for high performance and low power consumption, utilizing sophisticated architecture and advanced technology.

- Fabricated in TSMC’s 12nm CMOS process, this solution includes both controller and PHY IPs, providing comprehensive support for DDR3 and DDR4 memory interfaces.

-

Intel® FPGA IP for DDR3 SDRAM High-Performance Controller

- The Intel FPGA Intellectual Property (IP) for DDR3 SDRAM High-Performance Controller provides simplified interfaces to industry-standard DDR3 SDRAM devices and modules

- The Intel FPGA IP work in conjunction with the Intel FPGA ALTMEMPHY physical interface IP

- These DDR3 SDRAM IP functions offer a half-rate interface to the customer application logic.

-

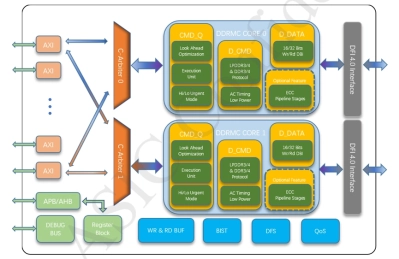

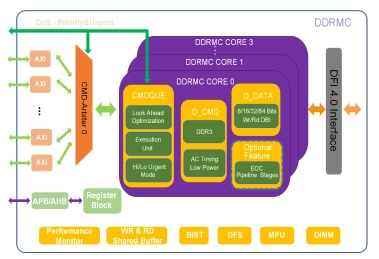

DDR3 IP solution

- Compatible with DDR3 up to 2133Mbps

- AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- DFI compliant interface between controller and PHY

- Support ECC (error correcting code)

-

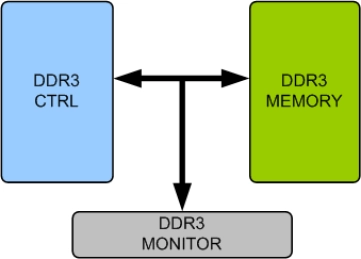

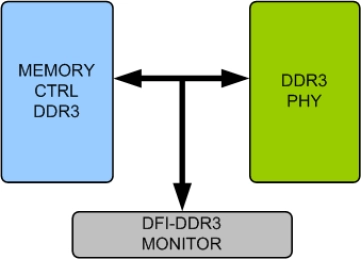

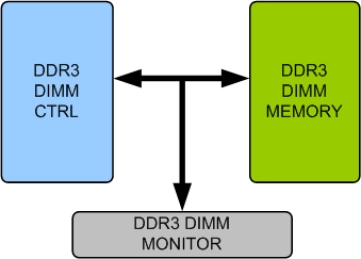

DDR3 Monitor Verification IP

- Supports DDR3 memory devices from all leading vendors

- Quickly validates the implementation of the DDR3 standard

- Constantly monitors DDR3 behavior during simulation

- Checks for following

-

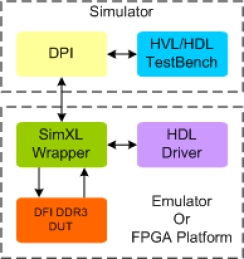

DDR3 DFI Synthesizable Transactor

- Compliant with DFI version 2.0 or higher Specifications.

- DFI-DDR3 Applies to :

- DDR3 protocol standard JESD79-3F Specification

- Supports all the Interface Groups.

-

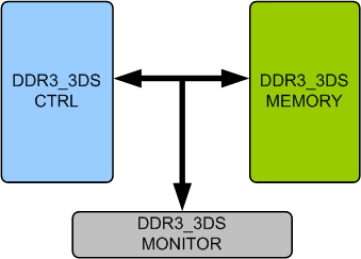

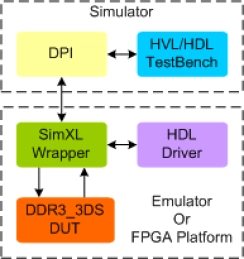

DDR3 3DS Synthesizable Transactor

- Supports 100% of DDR3 3DS protocol standard JESD79-3-3

- Supports all the DDR3 3DS commands as per the specs

- Supports up to 64GB device density

- Supports 64 internal banks

-

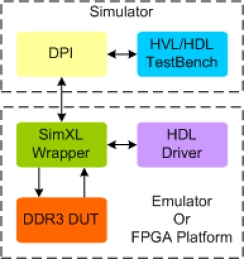

DDR3 Synthesizable Transactor

- Supports 100% of DDR3 protocol standard JESD79-3F

- Supports all the DDR3 commands as per the specs

- Supports up to 8 GB device density:

- Supports following devices:

-

DDR3 DFI Verification IP

- Compliant with DFI version 2.0 or higher Specifications.

- DFI-DDR3 Applies to :

- DDR3 protocol standard JESD79-3F Specification

- Supports all the Interface Groups.

-

DDR3 DIMM Memory Model

- Supports DDR3 DIMM memory devices from all leading vendors.

- Supports 100% of DDR3 DIMM protocol standard.

- Supports DDR3 UDIMM, RDIMM and LRDIMM types.

- Supports all the DDR3 DRAM features.

-

DDR3 3DS Memory Model

- Supports DDR3 3DS memory devices from all leading vendors.

- Supports 100% of DDR3 3DS protocol standard JESD79-3-3.

- Supports all the DDR3 3DS commands as per the specs.

- Supports up to 64GB device density.